anhnha

Full Member level 6

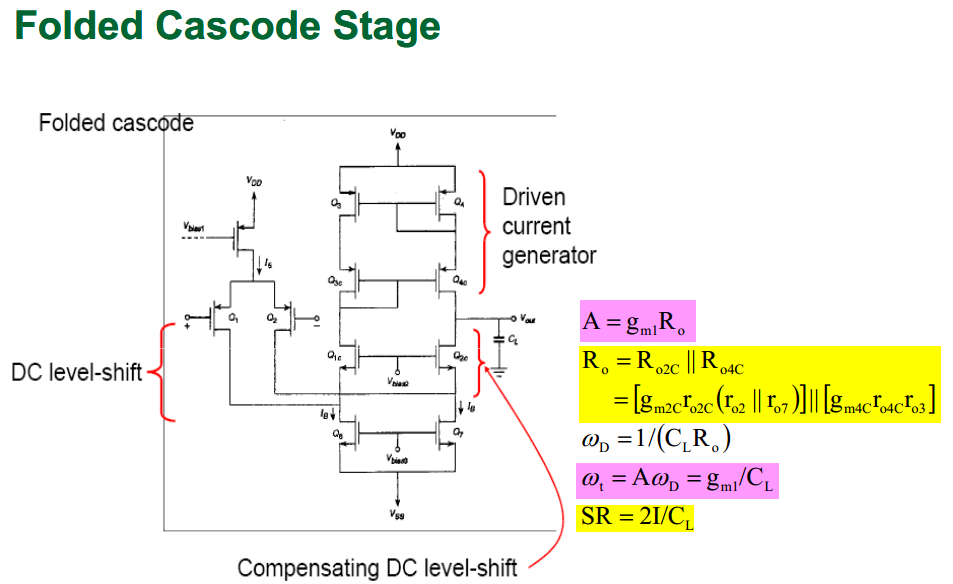

I saw this picture of folded cascode amplifier somewhere in a slide lecture. The problem is that the writer didn't give any explanation about subblocks in the picture.

As you can see, there are blocks:

- DC shift level

- Compensating DC shift level

- Driven current generator

I have searched a lot for how these blocks work but found nothing.

Could you please, explain how they work or give some links with explanations?

Thank you.

As you can see, there are blocks:

- DC shift level

- Compensating DC shift level

- Driven current generator

I have searched a lot for how these blocks work but found nothing.

Could you please, explain how they work or give some links with explanations?

Thank you.