kathmandu

Full Member level 5

Hello,

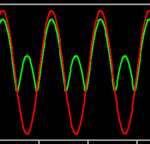

What could be a simple method to detect flux imbalance (DC build-up)?

I need to measure it for a low-frequency transfomer connected to a Mosfet full-bridge (driven by an unipolar SPWM signal).

It's a high power sine wave inverter and I've noticed a strange behaviour (even with light resistive load).

The transformer is making an uniform growing (buzzing) noise then it suddenly stops and the whole process it's restarting over and over again (with a period of ~ 3 seconds).

I can't put a capacitor in series with the transformer as there are high currents involved (> 100 A).

I've tried to generate a perfectly symetrical PWM signal and to use identical gate drivers/Mosfets for all the bridge switches but still I have this issue.

I only have a voltage-control loop, to change the SPWM duty cycle factor according to the load current.

To avoid this flux walking, I was checking/changing the PWM duty-cycle at the same point (after the same zero-crossing) to always have full waves (same number of positive and negative half waves) driven by an identical PWM signal.

I wonder if I could detect this flux imbalance (DC build-up) by doing some measurements of the transformer primary voltage (full-bridge switching nodes).

Maybe I could rectify & filter both node signals then (by using a comparator) I could check for any DC level differences?

I can use such a signal to tell the MCU to attenuate the PWM signal for a specific half wave only.

Also, I wonder what is "reseting" the flux imbalance for now, as I don't have any current-control loop or something.

Thanks in advance for any clue.

PS: There are some periods of time when the transformer is not making any noise though. Maybe it's something software related (PWM generation) but still I want to be able to check that flux imbalance with an external circuit.

What could be a simple method to detect flux imbalance (DC build-up)?

I need to measure it for a low-frequency transfomer connected to a Mosfet full-bridge (driven by an unipolar SPWM signal).

It's a high power sine wave inverter and I've noticed a strange behaviour (even with light resistive load).

The transformer is making an uniform growing (buzzing) noise then it suddenly stops and the whole process it's restarting over and over again (with a period of ~ 3 seconds).

I can't put a capacitor in series with the transformer as there are high currents involved (> 100 A).

I've tried to generate a perfectly symetrical PWM signal and to use identical gate drivers/Mosfets for all the bridge switches but still I have this issue.

I only have a voltage-control loop, to change the SPWM duty cycle factor according to the load current.

To avoid this flux walking, I was checking/changing the PWM duty-cycle at the same point (after the same zero-crossing) to always have full waves (same number of positive and negative half waves) driven by an identical PWM signal.

I wonder if I could detect this flux imbalance (DC build-up) by doing some measurements of the transformer primary voltage (full-bridge switching nodes).

Maybe I could rectify & filter both node signals then (by using a comparator) I could check for any DC level differences?

I can use such a signal to tell the MCU to attenuate the PWM signal for a specific half wave only.

Also, I wonder what is "reseting" the flux imbalance for now, as I don't have any current-control loop or something.

Thanks in advance for any clue.

PS: There are some periods of time when the transformer is not making any noise though. Maybe it's something software related (PWM generation) but still I want to be able to check that flux imbalance with an external circuit.

Last edited: