WBrumble

Junior Member level 3

All,

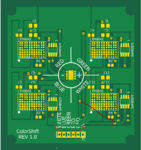

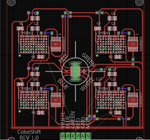

This is my first PCB build and I've got some questions before finalizing and moving to fabrication.

It's a 2 layer board, with led drivers (for RGBW), 12 volt supply, LED drivers running at 2mhz, and a maximum of 4 amps, 1 amp per color die.

The inputs at the bottom are; White, Red, Green, Blue are PWM inputs, and VCC/GND.

Board outline dimensions 3 3/16"x 3"

Two questions I have:

- Do I need to worry about EMI at 2mhz?

- What spacing for ground vias do I use between to top and bottom layer ground pours?

One more question not really related directly to the PCB design, could someone point me to a good read for thermodynamics and heatsink calculations/design.

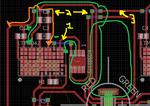

Here are exported photos from eagle of the top and bottom of the board "if you see any issues please let me know":

Thank you guys in advance for the help!

This is my first PCB build and I've got some questions before finalizing and moving to fabrication.

It's a 2 layer board, with led drivers (for RGBW), 12 volt supply, LED drivers running at 2mhz, and a maximum of 4 amps, 1 amp per color die.

The inputs at the bottom are; White, Red, Green, Blue are PWM inputs, and VCC/GND.

Board outline dimensions 3 3/16"x 3"

Two questions I have:

- Do I need to worry about EMI at 2mhz?

- What spacing for ground vias do I use between to top and bottom layer ground pours?

One more question not really related directly to the PCB design, could someone point me to a good read for thermodynamics and heatsink calculations/design.

Here are exported photos from eagle of the top and bottom of the board "if you see any issues please let me know":

Thank you guys in advance for the help!

Last edited: