TnF

Junior Member level 3

I am making a custom keyboard with an integrated usb hub and 2 input/upstream usb type-c ports (selectable).

So my first prototype board had some issues with usb connectivity due to me not knowing anything about differential pair routing, matching/coupling and impedance control. I've learnt about it now and using my pcb specs (1.6mm thick, 1.52mm fr-4, 1oz cooper) and a target of 90ohm differential impedance, i calculated a value of about 0.93mm track width with 5mil spacing. Then i tried routing the differential pairs as best as i can, and after playing with component placement and much manual routing i was able to route the whole board.

This is not the final routing but i made many changes to the pcb and schematic and i wanted to know beforehand if it is possible to route it without:

a) Changing the board size

b) Going with a 4-layer board

For (a) i tried to keep the same size due to the reason being that i want it to be as compact as possible (also this needs less changes to be made after like the case and plate) and solderable by the tools i have, and for (b) the reason is that 4-layer is twice as expensive, and jlcpcb can't make it due to being over 300mm (mine being over 350mm in length of which i cannot change). I know pcb-way can make it but i don't want to spend additional money for a prototype i will be probably the only one using, and i was really happy with jlcpcb service.

So lets start:

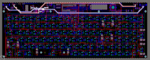

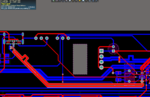

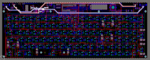

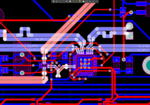

Here is the overall board without any overlays. You can see i have a total of 7 differential pairs, some of which span more than 250mm in length.

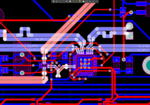

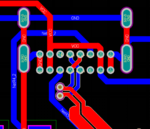

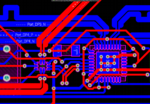

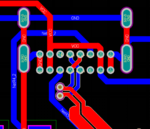

Here is where all the pairs end up. On the left we have a USB switch controller which connects a 4-port USB hub controller on the right. The job of the USB switch is to select either the left or right USB-C port which interfaces to the host device and connect it to the hub.

First question: Note that i had to fanout the pairs with thinner traces (0.35mm, 5mil spacing). Is that an issue or not? Is there is a better way considering the 2-layer board limitations?

Also the usb switch is connected to the usb hub with 0.35mm traces only. Still gapped to the min possible by jlcpcb (5mils). They are about 14mm in length and i had do these flip shenanigans. I've tried changing ports to minimise flipping but it was inevitable i had to flip some signals. Would this be problematic?

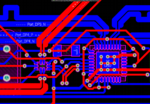

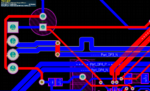

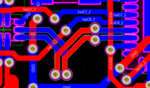

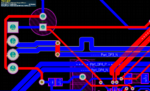

Here we can see the track thickness transition from one of the fanouts. Is that as bad as it looks or no? (ignore the non differential pair tracks as i did 0 cleanup on this board)

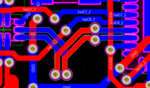

Here is one long pair. I did length matching to all, but i generally had to do it where the traces are the 0.93mm thick ones. This makes a big kink where it leaves a small section of the track uncoupled with the other one. Would that cause an issue, and can be improved upon? (I tried to make the kink gap as small as possible)

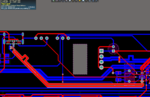

Here's a close-up of my shenanigans with the usb-c port. The other one is better because it didn't require a signal flip. Can i do better?

Here is one other type of shenanigan i had to make (i believe is the only one like this). Will it work or not?

Finally the last thing i want to ask is regarding the copper pours. In my first board i had a ground fill plane on the bottom layer, and a VCC fill plane on the top layer. Reasoning is that most components are on the bottom and are fairly low power so i used it for ground distribution, and on the top layer for power distribution to the over 100 rgb leds i have daisy chained. Is this ok to do for differential pair shielding or should both be ground pours instead?

My theory is that EMI doesn't care at what DC level a plane is at, and since both are at constant values, the electromagnetic field between them while it will not be zero it will be constant and non-changing to affect the signals. I may be mistaken though.

ps: All signals are to support USB 2.0 hi-speed 480mbps.

ps 2: Instead of routing i believe it is way more easier to have these pairs (at least the long ones) to be connected via a bodge twisted wire instead. Is this an acceptable method?

So my first prototype board had some issues with usb connectivity due to me not knowing anything about differential pair routing, matching/coupling and impedance control. I've learnt about it now and using my pcb specs (1.6mm thick, 1.52mm fr-4, 1oz cooper) and a target of 90ohm differential impedance, i calculated a value of about 0.93mm track width with 5mil spacing. Then i tried routing the differential pairs as best as i can, and after playing with component placement and much manual routing i was able to route the whole board.

This is not the final routing but i made many changes to the pcb and schematic and i wanted to know beforehand if it is possible to route it without:

a) Changing the board size

b) Going with a 4-layer board

For (a) i tried to keep the same size due to the reason being that i want it to be as compact as possible (also this needs less changes to be made after like the case and plate) and solderable by the tools i have, and for (b) the reason is that 4-layer is twice as expensive, and jlcpcb can't make it due to being over 300mm (mine being over 350mm in length of which i cannot change). I know pcb-way can make it but i don't want to spend additional money for a prototype i will be probably the only one using, and i was really happy with jlcpcb service.

So lets start:

Here is the overall board without any overlays. You can see i have a total of 7 differential pairs, some of which span more than 250mm in length.

Here is where all the pairs end up. On the left we have a USB switch controller which connects a 4-port USB hub controller on the right. The job of the USB switch is to select either the left or right USB-C port which interfaces to the host device and connect it to the hub.

First question: Note that i had to fanout the pairs with thinner traces (0.35mm, 5mil spacing). Is that an issue or not? Is there is a better way considering the 2-layer board limitations?

Also the usb switch is connected to the usb hub with 0.35mm traces only. Still gapped to the min possible by jlcpcb (5mils). They are about 14mm in length and i had do these flip shenanigans. I've tried changing ports to minimise flipping but it was inevitable i had to flip some signals. Would this be problematic?

Here we can see the track thickness transition from one of the fanouts. Is that as bad as it looks or no? (ignore the non differential pair tracks as i did 0 cleanup on this board)

Here is one long pair. I did length matching to all, but i generally had to do it where the traces are the 0.93mm thick ones. This makes a big kink where it leaves a small section of the track uncoupled with the other one. Would that cause an issue, and can be improved upon? (I tried to make the kink gap as small as possible)

Here's a close-up of my shenanigans with the usb-c port. The other one is better because it didn't require a signal flip. Can i do better?

Here is one other type of shenanigan i had to make (i believe is the only one like this). Will it work or not?

Finally the last thing i want to ask is regarding the copper pours. In my first board i had a ground fill plane on the bottom layer, and a VCC fill plane on the top layer. Reasoning is that most components are on the bottom and are fairly low power so i used it for ground distribution, and on the top layer for power distribution to the over 100 rgb leds i have daisy chained. Is this ok to do for differential pair shielding or should both be ground pours instead?

My theory is that EMI doesn't care at what DC level a plane is at, and since both are at constant values, the electromagnetic field between them while it will not be zero it will be constant and non-changing to affect the signals. I may be mistaken though.

ps: All signals are to support USB 2.0 hi-speed 480mbps.

ps 2: Instead of routing i believe it is way more easier to have these pairs (at least the long ones) to be connected via a bodge twisted wire instead. Is this an acceptable method?