vug

Newbie

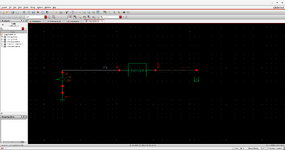

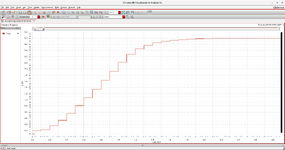

In the simulation output of this switched capacitor charge pump (attached below) , how to find the time constant?

Should the find the circuit time constant or is there time constant for each step in the transient?

Please help me with it. (I simulated the circuit in discrete z domain).

Should the find the circuit time constant or is there time constant for each step in the transient?

Please help me with it. (I simulated the circuit in discrete z domain).