pashkatarakashka

Newbie

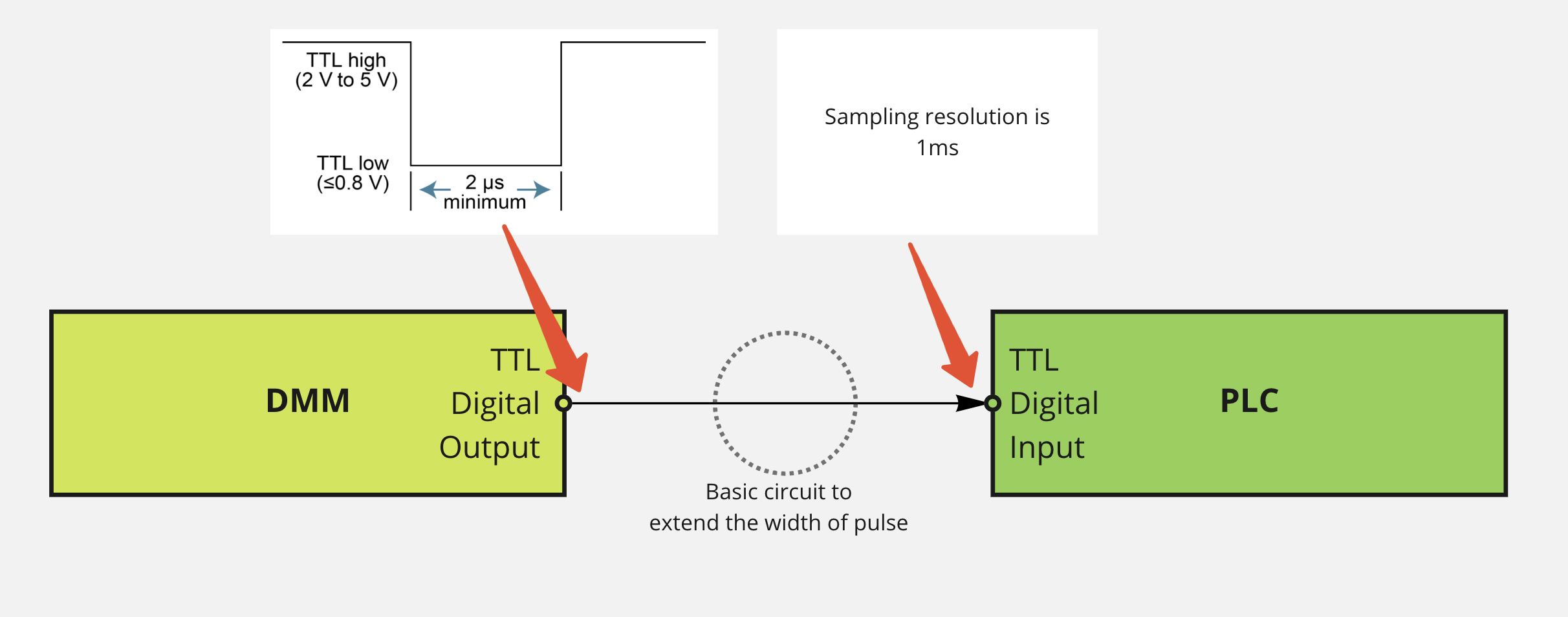

I have DMM which is producing pulse with duration of around few microseconds.

The pulse need to be sampled in PLC, which has sampling rate of 1ms.

In other words the cycle loop can't be reduced to microsecond resolution.

So it's impossible to reliably detect the pulse from DMM.

Could somebody recommend a simple TTL based circuit solution, which will be able to capture that microsecond resolution pulse and convert it into millisecond resolution pulse?

The pulse need to be sampled in PLC, which has sampling rate of 1ms.

In other words the cycle loop can't be reduced to microsecond resolution.

So it's impossible to reliably detect the pulse from DMM.

Could somebody recommend a simple TTL based circuit solution, which will be able to capture that microsecond resolution pulse and convert it into millisecond resolution pulse?