adnan012

Advanced Member level 1

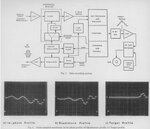

I need the explanation of the attached diagram. What is the working principle ?

What is the the delay block? How delay is achieved ?

The diagram is taken from the link.

***.semanticscholar.org/paper/A-Guided-Radar-System-for-Obstacle-Detection-Patfterson-Mackay/8a9776e710a4b0a432c48e4bf3da16f19f986e23

What is the the delay block? How delay is achieved ?

The diagram is taken from the link.

***.semanticscholar.org/paper/A-Guided-Radar-System-for-Obstacle-Detection-Patfterson-Mackay/8a9776e710a4b0a432c48e4bf3da16f19f986e23