Heena09

Junior Member level 3

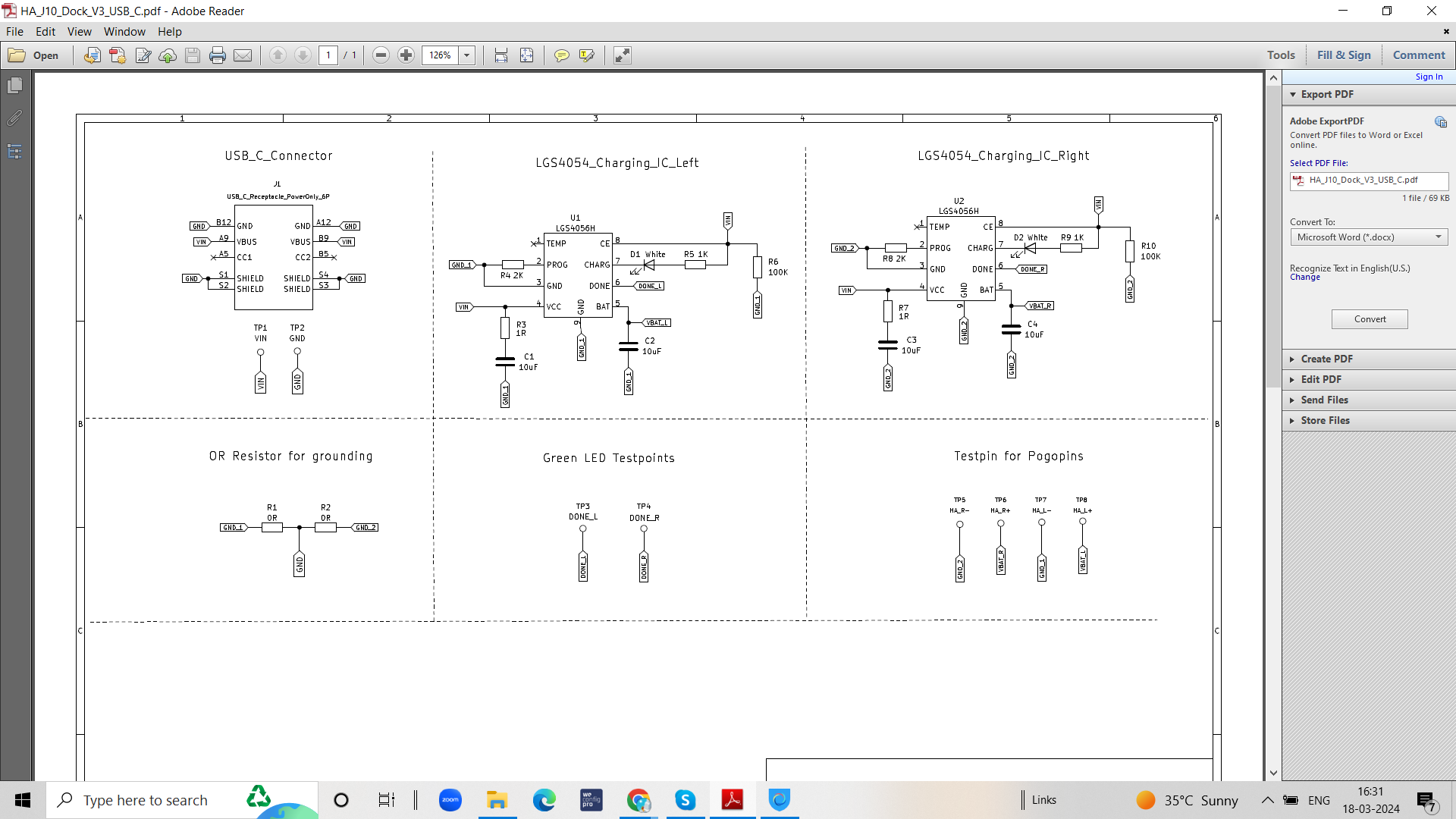

We are working on Charging Dock one of my hoby poject where we are using one of the Charging IC LGS4056

I used 2 Pogo pin to charge my device. But due to some issue this IC got damanged some time.

Do i need to add some protection ic in desgin at USB and Pogo pin side .

I used 2 Pogo pin to charge my device. But due to some issue this IC got damanged some time.

Do i need to add some protection ic in desgin at USB and Pogo pin side .