theguardian2001

Newbie level 6

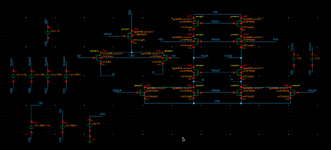

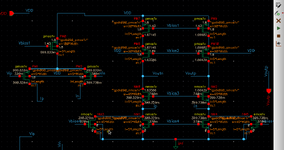

Hi everyone! I can say that I am relatively new in Cadence and I am currently migrating there from Spice. I was trying to simulate a dif. amplifier in gpdk90nm and have run into some problems. First of all, when I tried to simulate the schematic it has run into convergence errors and inability to compute an operating point (please see spectre_1.out in attachment). I am also attaching a log file (Job5) in case it is needed.

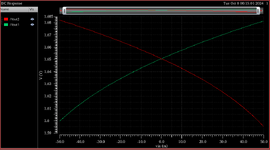

After several attempts I created a cellview from my schematic and provided power and input connections "on top" of it (by placing the created cell into a new cellview). The same simulation completed without any errors but the warnings appeared are crucial for the design:

Warning from spectre.

WARNING (CMI-2477): I0.PM0: `Rds' = 433.574 nOhm is less than 0.001. Set to 0.

WARNING (CMI-2477): I0.PM1: `Rds' = 15.9184 uOhm is less than 0.001. Set to 0.

WARNING (CMI-2477): I0.PM8: `Rds' = 867.631 nOhm is less than 0.001. Set to 0.

This basically implies that PMOSes does not contribute to output impedance thus ruining the overall gain. (Please see spectre_2.out). I would really appreciate any help and hints which can help me (and probably others in the future) to resolve the issue. The schematic is attached as a picture as well (Constant voltage sources were placed instead of a full bias circuitry - which has been tested without errors but with the same warnings - to reduce the complexity of the netlist file).

In case if anybody knows what causes Spectre to run the simulations with a symbol but not the schematic and why do only 3 PMOSes suffer from from low output impedance - I would also highly appreciate any explanation or advice regarding this issue to be able to resolve it in future.

Thanks everyone in advance

After several attempts I created a cellview from my schematic and provided power and input connections "on top" of it (by placing the created cell into a new cellview). The same simulation completed without any errors but the warnings appeared are crucial for the design:

Warning from spectre.

WARNING (CMI-2477): I0.PM0: `Rds' = 433.574 nOhm is less than 0.001. Set to 0.

WARNING (CMI-2477): I0.PM1: `Rds' = 15.9184 uOhm is less than 0.001. Set to 0.

WARNING (CMI-2477): I0.PM8: `Rds' = 867.631 nOhm is less than 0.001. Set to 0.

This basically implies that PMOSes does not contribute to output impedance thus ruining the overall gain. (Please see spectre_2.out). I would really appreciate any help and hints which can help me (and probably others in the future) to resolve the issue. The schematic is attached as a picture as well (Constant voltage sources were placed instead of a full bias circuitry - which has been tested without errors but with the same warnings - to reduce the complexity of the netlist file).

In case if anybody knows what causes Spectre to run the simulations with a symbol but not the schematic and why do only 3 PMOSes suffer from from low output impedance - I would also highly appreciate any explanation or advice regarding this issue to be able to resolve it in future.

Thanks everyone in advance