mohamis288

Full Member level 3

Hello,

I have created a FIR_Filter verilog code and I want to synthesize my code in Synopsys software.

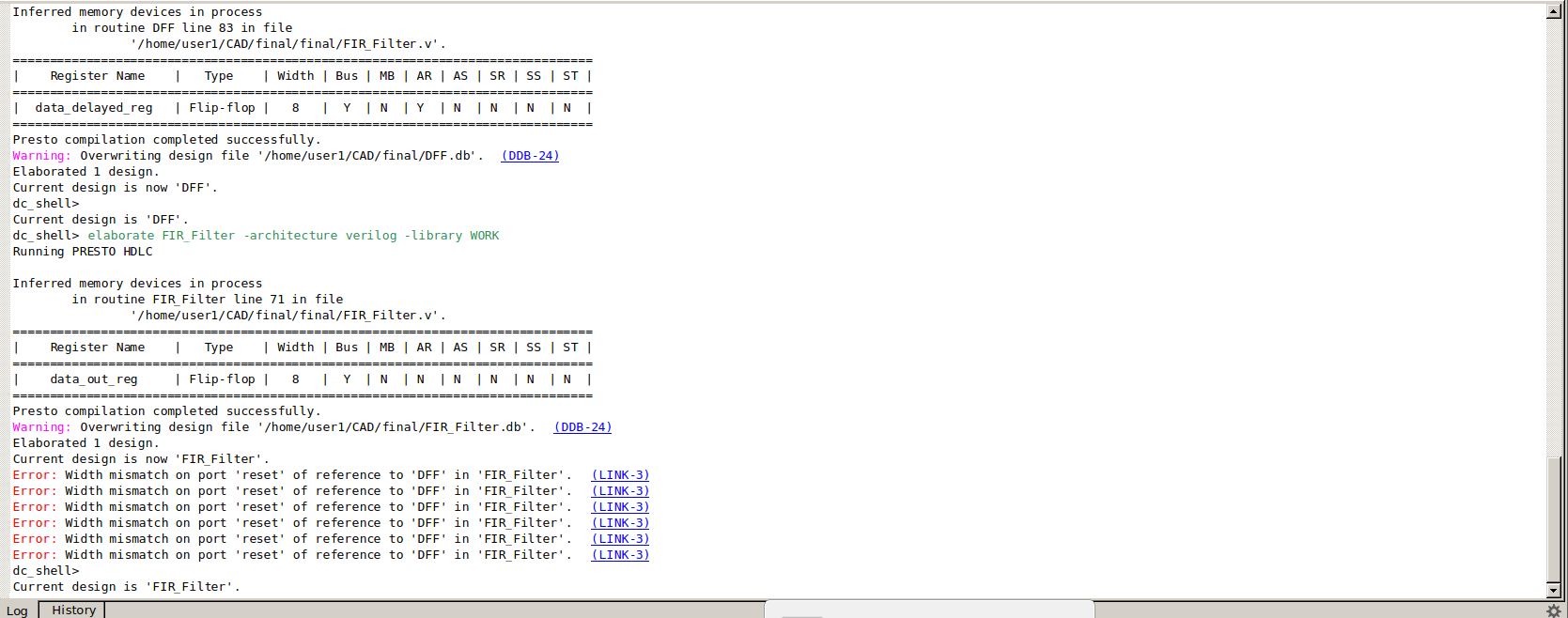

But When I want to elaborate my Verilog code, the following Error shown:

What is the problem?

My verilog code is present in the attachment.

I have created a FIR_Filter verilog code and I want to synthesize my code in Synopsys software.

But When I want to elaborate my Verilog code, the following Error shown:

What is the problem?

My verilog code is present in the attachment.

Code Verilog - [expand]

Attachments

Last edited by a moderator: