omarelmorsy

Junior Member level 1

hello,

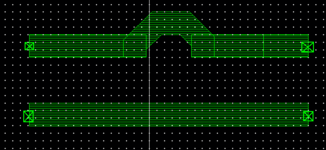

I have created an inductor on metal 9 and a ground plane (return path) on metal 3 as in image1.

The inductor value is intended to be around 80pf, and the inductance value turns to be what I intended, however the quality factor of the inductor is so small around ( 5 ).

the ports used are +-1 and +-2 boxwall ports.

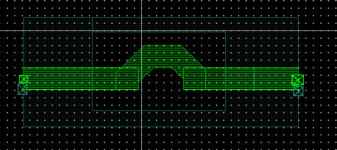

However when I used the return path as a ground rail as in image 2 the quality factor jumps up to 30.

I think there might be a problem with the eming process.

I know that having ground planes for the RF circuits are better than ground rails for less overall noise and better grounding, however this gives me worse quality factor for my inductors.

note: image 1 that is containing ground plane is a part (cut out) from a bigger circuit.

I have created an inductor on metal 9 and a ground plane (return path) on metal 3 as in image1.

The inductor value is intended to be around 80pf, and the inductance value turns to be what I intended, however the quality factor of the inductor is so small around ( 5 ).

the ports used are +-1 and +-2 boxwall ports.

However when I used the return path as a ground rail as in image 2 the quality factor jumps up to 30.

I think there might be a problem with the eming process.

I know that having ground planes for the RF circuits are better than ground rails for less overall noise and better grounding, however this gives me worse quality factor for my inductors.

note: image 1 that is containing ground plane is a part (cut out) from a bigger circuit.