yefj

Advanced Member level 5

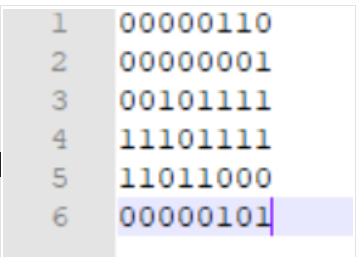

Hello,I am trying to communincate using SPI protocol and send the pattern bellow with manual rise of Chip Select between every command of the 6 commands.

As you can see bellow i managed to send all six bytes at once as you can see bellow.

I was imagining to see the CS Rise between them with the same width of 1 bit as in the MOSI pattern .

But in reality i get CS jump with some glitch like pattern, and they are not between the commands

The full code is attached bellow.

Where did i go wrong implementing the manual Chip select?

Thanks.

As you can see bellow i managed to send all six bytes at once as you can see bellow.

I was imagining to see the CS Rise between them with the same width of 1 bit as in the MOSI pattern .

But in reality i get CS jump with some glitch like pattern, and they are not between the commands

The full code is attached bellow.

Where did i go wrong implementing the manual Chip select?

Thanks.

Code:

/**************************************************************************//**

* @main_series1_PG1_EFR.c

* @brief Demonstrates USART1 as SPI master.

* @version 0.0.2

******************************************************************************

* @section License

* <b>Copyright 2018 Silicon Labs, Inc. http://www.silabs.com</b>

*******************************************************************************

*

* This file is licensed under the Silabs License Agreement. See the file

* "Silabs_License_Agreement.txt" for details. Before using this software for

* any purpose, you must agree to the terms of that agreement.

*

******************************************************************************/

#include "em_device.h"

#include "em_chip.h"

#include "em_cmu.h"

#include "em_gpio.h"

#include "em_usart.h"

#include "em_ldma.h"

#define TX_WREN_BUFFER_SIZE 1

#define TX_WRSR_BUFFER_SIZE 4

#define TX_RDSR_BUFFER_SIZE 1

#define RX_BUFFER_SIZE 1

uint8_t Tx_WREN[TX_WREN_BUFFER_SIZE] = {0x06};//write enable command

uint8_t Tx_WRSR[TX_WRSR_BUFFER_SIZE] = {0x01,0x2F,0xEF,0xD8}; //write status register

uint8_t Tx_RDSR[TX_RDSR_BUFFER_SIZE] = {0x05}; //read status register

uint32_t TxBufferIndex = 0;

uint32_t RxBuffer;

//uint32_t RxBufferIndex = 0;

volatile uint32_t msTicks; /* counts 1ms timeTicks */

void Delay(uint32_t dlyTicks);

void SysTick_Handler(void)

{

msTicks++; /* increment counter necessary in Delay()*/

}

void Delay(uint32_t dlyTicks)

{

uint32_t curTicks;

curTicks = msTicks;

while ((msTicks - curTicks) < dlyTicks) ;

}

int main(void)

{

CHIP_Init();

CMU_ClockEnable(cmuClock_GPIO, true);

CMU_ClockEnable(cmuClock_USART1, true);

CMU_ClockEnable(cmuClock_USART0, true);

// Configure GPIO mode

GPIO_PinModeSet(gpioPortC, 8, gpioModePushPull, 0); // US1_CLK is push pull

GPIO_PinModeSet(gpioPortA, 4, gpioModePushPull, 1); // US1_CS is push pull

GPIO_PinModeSet(gpioPortC, 6, gpioModePushPull, 1); // US1_TX (MOSI) is push pull

GPIO_PinModeSet(gpioPortC, 7, gpioModeInput, 1); // US1_RX (MISO) is input

// Start with default config, then modify as necessary

USART_InitSync_TypeDef config = USART_INITSYNC_DEFAULT;

config.master = true; // master mode

config.baudrate = 1000000; // CLK freq is 1 MHz

config.autoCsEnable = false; // CS pin controlled by firmware, not hardware

config.clockMode = usartClockMode0; // clock idle low, sample on rising/first edge

config.msbf = true; // send MSB first

config.enable = usartDisable; // Make sure to keep USART disabled until it's all set up

USART_InitSync(USART1, &config);

USART_InitAsync_TypeDef init = USART_INITASYNC_DEFAULT;

// set pin modes for UART TX and RX pins

GPIO_PinModeSet(gpioPortA, 1, gpioModeInput, 1);

GPIO_PinModeSet(gpioPortA, 0, gpioModePushPull, 1);

///////////////////////////////////

USART_InitAsync(USART0, &init);

USART0->ROUTELOC0 =(USART_ROUTELOC0_TXLOC_LOC0) | // US1_TX (MOSI) on location 11 = PC6 per datasheet section 6.4 = EXP Header pin 4

(USART_ROUTELOC0_RXLOC_LOC0); // US1_RX (MISO) on location 11 = PC7 per datasheet section 6.4 = EXP Header pin 6

// Set USART pin locations

USART1->ROUTELOC0 = (USART_ROUTELOC0_CLKLOC_LOC11) | // US1_CLK on location 11 = PC8

(USART_ROUTELOC0_CSLOC_LOC11) | // US1_CS Manual

(USART_ROUTELOC0_TXLOC_LOC11) | // US1_TX (MOSI) on location 11 = PC6

(USART_ROUTELOC0_RXLOC_LOC11); // US1_RX (MISO) on location 11 = PC7

// Enable USART pins

USART1->ROUTEPEN = USART_ROUTEPEN_CLKPEN | USART_ROUTEPEN_TXPEN | USART_ROUTEPEN_RXPEN;

// Enable USART1

USART_Enable(USART1, usartEnable);

TxBufferIndex = 0;

while(1)

{

// Write enable command

GPIO_PinOutClear(gpioPortA,4);

USART_Tx(USART1, Tx_WREN[0]);

GPIO_PinOutSet(gpioPortA,4);

GPIO_PinOutClear(gpioPortA,4);

USART_Tx(USART1, Tx_WRSR[0]);

USART_Tx(USART1, Tx_WRSR[1]);

USART_Tx(USART1, Tx_WRSR[2]);

USART_Tx(USART1, Tx_WRSR[3]);

GPIO_PinOutSet(gpioPortA,4);

GPIO_PinOutClear(gpioPortA,4);

USART_Tx(USART1, Tx_RDSR[0]);

RxBuffer = USART_Rx(USART1);

GPIO_PinOutSet(gpioPortA,4);

// USART_Tx(USART0,RxBuffer);

// USART_Tx(USART0, '\n');

}

}

Last edited: