Mvitale

Newbie

I'm a PhD student and I'm dealing with the design of an ADC pipeline 10 bit, 50 Msps:

four 2.5bit stage and last 2 bit Flash.

This is the 2.5bit stage, The OTA is a pseudodifferential ring Amp.:

In order to take in to account the effect of the parasitic capacitances and inductances of the bonding wire on the power supply, I implemented a simple model showed below:

vdd and gnd power the ADC circuit.

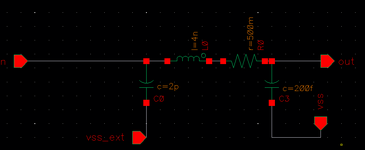

Inside the box there is the following circuit:

where vss_ext is the external ground, and vss is the internal ground of the circuit.

It is a common model that I observe in many paper.

This is the residium of the first stage with "ideal" power supply without the PAD effect.

When I include the bonding wire circuit (that I showed up) the residium start to oscillate:

This happened for all the stages.

The problem is the inductances on the power supply:

Indeed, if I reduce the nominal value, the oscillation decrease.

The only way I've found to reduce oscillations is to put multiple bonding wires in parallel, implementing the following model:

But I dont know if it is feasible this solution.

Do you have any other ideas regarding this problem?

Really Sorry if I wasn't very clear in describing the problem, if necessary I'm available to answer your questions.

four 2.5bit stage and last 2 bit Flash.

This is the 2.5bit stage, The OTA is a pseudodifferential ring Amp.:

In order to take in to account the effect of the parasitic capacitances and inductances of the bonding wire on the power supply, I implemented a simple model showed below:

vdd and gnd power the ADC circuit.

Inside the box there is the following circuit:

where vss_ext is the external ground, and vss is the internal ground of the circuit.

It is a common model that I observe in many paper.

This is the residium of the first stage with "ideal" power supply without the PAD effect.

When I include the bonding wire circuit (that I showed up) the residium start to oscillate:

This happened for all the stages.

The problem is the inductances on the power supply:

Indeed, if I reduce the nominal value, the oscillation decrease.

The only way I've found to reduce oscillations is to put multiple bonding wires in parallel, implementing the following model:

But I dont know if it is feasible this solution.

Do you have any other ideas regarding this problem?

Really Sorry if I wasn't very clear in describing the problem, if necessary I'm available to answer your questions.