kaiserschmarren87

Member level 4

- Joined

- May 15, 2013

- Messages

- 75

- Helped

- 9

- Reputation

- 18

- Reaction score

- 9

- Trophy points

- 1,288

- Location

- Germany

- Activity points

- 1,838

I wasn't suggesting that the transceivers don't work at 4.2 line rate. My guess it has something to do with when you perform the reference clock frequency switch. That is why in one suggestion I made early you might want to try different reset sequencing. It seems to me that the transceiver may not be starting up correctly so can never synchronize to the input.

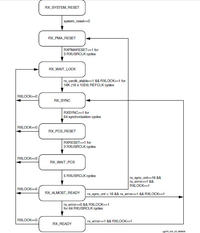

I am not sure whether PLL is getting locked to REFCLK. Looks like I need to check the RXLOCK parameter again for 4.2 gbps line rate. At present transceiver uses the reset sequence with RX Buffer. The state machine is designed in the current design is quite different from the FSM - GT11_RX.vhd of the rocket wrapper generated by the Core Generator but logic is the same.

This is the current reset sequencing fsm:

Should I test now by choosing transceiver to bypass the RX Buffer and use the below reset sequencing which puts RX_SYNC state.

I once tried gt11_rx.vhd fsm with RX_SYNC reset sequence but didn't work. Maybe I can give another try with this reset sequence and look for the difference.

8B/10B encoding is not used. I will attach the transceiver configuration which I did below.Never thought to ask but what is the protocol you are using for the links? Is it 8-bit data or 16-bit data, if you are using 16-bit data you should use two different K-codes for idle and alternate them. You should also make sure that the alignment never changes and that any insertion or deletion of symbols is done as pairs.

This is how the RX works in my design if I am not wrong since many parameters are just bypassed:

I did not know this. Since I am coming across this transceiver for the first time, I have encountered so much with Virtex 4 now which should be documented from my side atleast !You know all these problems you are contending with is the reason Xilinx only used this version of transceiver in a single product. The V5 has a different transceiver that has a much simpler configuration, without all the extra options that the V4 transceivers had. Both V6 & V7 have continued that trend so they are all much easier to use.

Attachments

Last edited: