Hjldioyitsi

Member level 1

I have two basic questions:

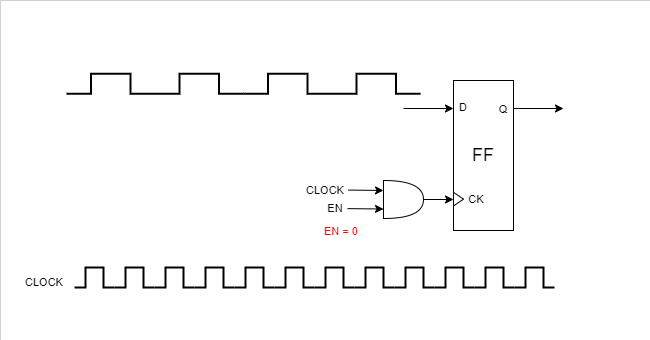

(1) If a basic D flip-flop has its clock gated-off, but it keeps "receiving" continuously toggling data at its D pin, will there be any dynamic power consumption? In such a (theoretical) scenario, would it make sense to also gate the D pin to logical 0 in order to reduce power?

(2) Which one does save more power? To gate-off the FF´s clock or to keep the FF in reset state? Or maybe both?

(1) If a basic D flip-flop has its clock gated-off, but it keeps "receiving" continuously toggling data at its D pin, will there be any dynamic power consumption? In such a (theoretical) scenario, would it make sense to also gate the D pin to logical 0 in order to reduce power?

(2) Which one does save more power? To gate-off the FF´s clock or to keep the FF in reset state? Or maybe both?