electroboy

Member level 5

hi...

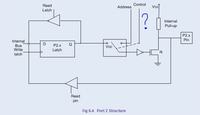

it is said that port 2 of 8051 has internal pull up in both functions (i.e when used as i/o or higher order address). but according to the figure given in manual, it is not possible for port 2 to have internal pull ups in both functions.

the control should be zero either during i/o or address operation. please help ... some websites show port 2 without that AND gate. which is correct?

also my question is, Should we use external pull up when using port 2 for higher order address ?

it is said that port 2 of 8051 has internal pull up in both functions (i.e when used as i/o or higher order address). but according to the figure given in manual, it is not possible for port 2 to have internal pull ups in both functions.

the control should be zero either during i/o or address operation. please help ... some websites show port 2 without that AND gate. which is correct?

also my question is, Should we use external pull up when using port 2 for higher order address ?

Last edited: