dipin

Full Member level 4

hi,

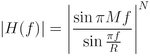

i just designed a cic filter to down sample input signals from 65 mhz to 10 khz. which will give a decimation factor of 6500.

i decided to implement this in cascaded manner :: that is 3 cic filter cascaded together which will have R:20,25 and 13 ?

where the max working register length is 38 bit width, if i selected 5 stages

now question is how can i select the NUMBER OF STAGES in the cic filter..?????

i read few articles and i didnt find any criteria for deciding N.. most of the papers they simply decided the N as 4,5 10 etc

and please excuse me if this is a stupid question

can anybody help me on this?

thanks and regards

i just designed a cic filter to down sample input signals from 65 mhz to 10 khz. which will give a decimation factor of 6500.

i decided to implement this in cascaded manner :: that is 3 cic filter cascaded together which will have R:20,25 and 13 ?

where the max working register length is 38 bit width, if i selected 5 stages

now question is how can i select the NUMBER OF STAGES in the cic filter..?????

i read few articles and i didnt find any criteria for deciding N.. most of the papers they simply decided the N as 4,5 10 etc

and please excuse me if this is a stupid question

can anybody help me on this?

thanks and regards