noor84

Member level 5

Hi all,

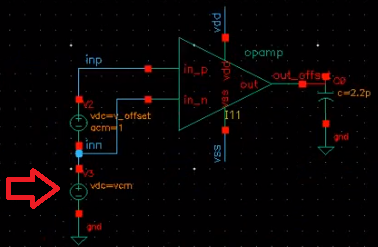

I am designing A two-stage OPAMP with double supply (vdd=2.5, vss=-2.5) using Cadence (Virtuoso),

The question is, in the simulation to find the output offset voltage, for example, should the DC voltage be 2.5V or 5V as shown in the attached picture), and why?

The same question is for all other measurements required such as common mode gain, CMRR, etc.

If I use one power supply, should the DC voltage be (1/2) vdd? and why?

Thanks in advance.

Continue to the question,

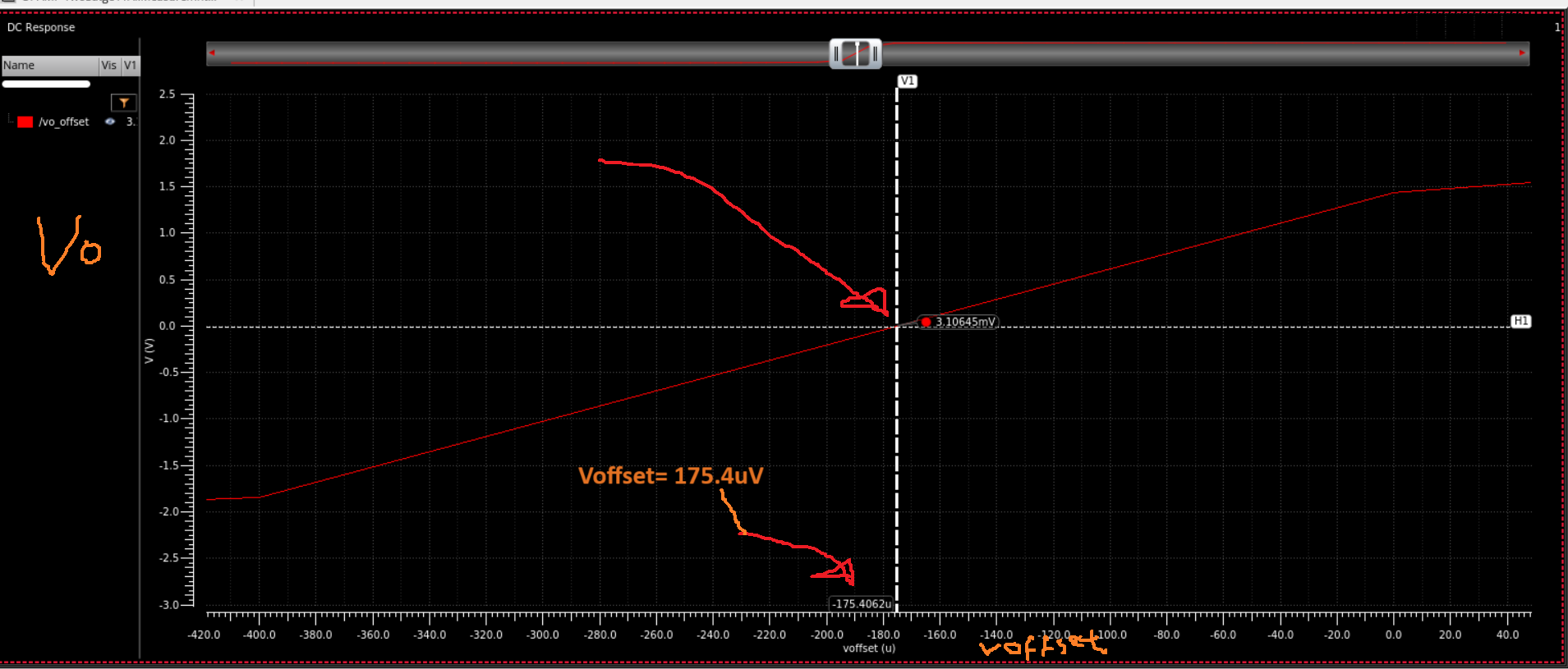

The result shown below is when the VCM(DC)=2.5V, then the Voltage offset is (175 uV), is that correct?

(This figure is maximize)

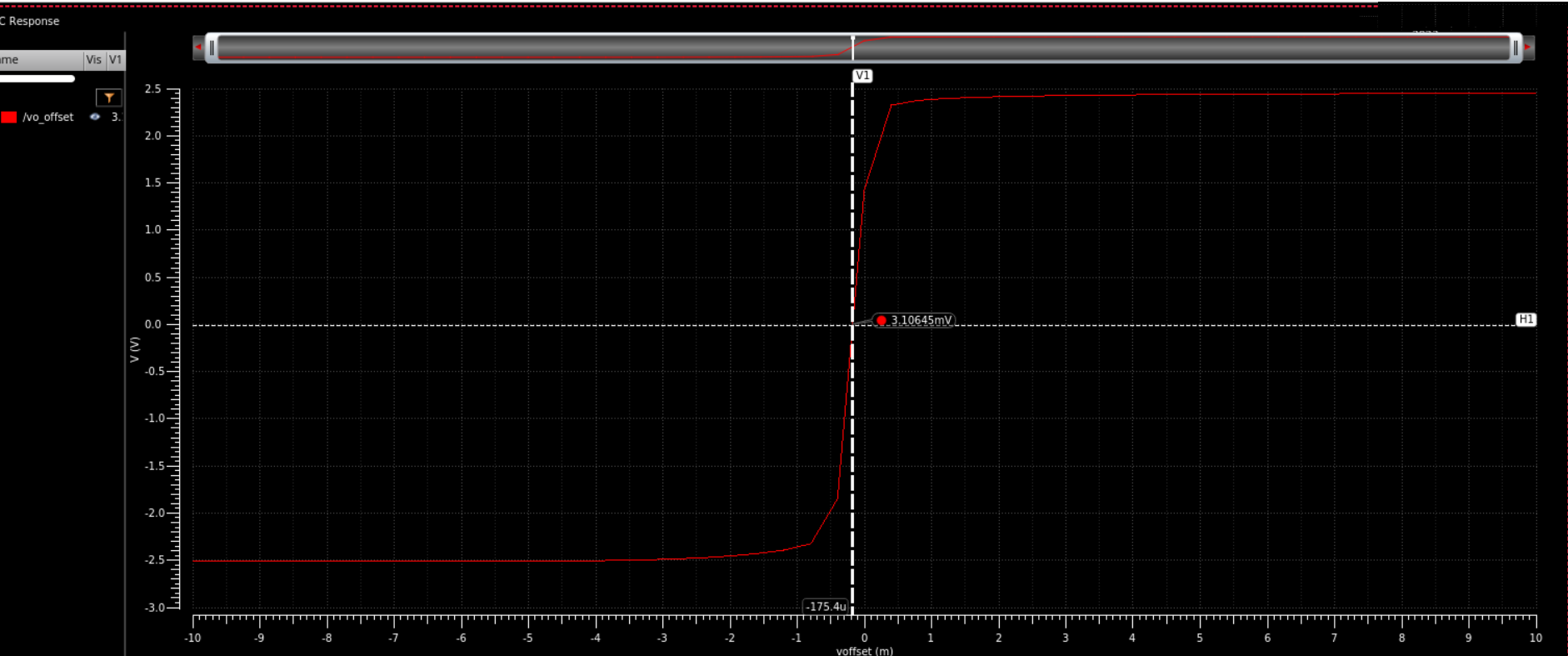

(The figure without Maximize)

I am designing A two-stage OPAMP with double supply (vdd=2.5, vss=-2.5) using Cadence (Virtuoso),

The question is, in the simulation to find the output offset voltage, for example, should the DC voltage be 2.5V or 5V as shown in the attached picture), and why?

The same question is for all other measurements required such as common mode gain, CMRR, etc.

If I use one power supply, should the DC voltage be (1/2) vdd? and why?

Thanks in advance.

--- Updated ---

Continue to the question,

The result shown below is when the VCM(DC)=2.5V, then the Voltage offset is (175 uV), is that correct?

(This figure is maximize)

(The figure without Maximize)

Last edited: