Hasan2017

Member level 4

Hi there,

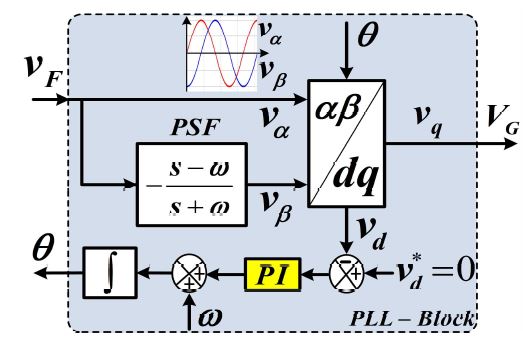

In order to achieve unity power factor control, the phase of the AC voltage needs to be obtained. The phase is obtained through a phase-locked loop (PLL).

Take a look for single phase control structure of the PLL ,

For such similar way I want to mention some of 3-phase equations, could you kindly elaborate it more ?

VSa = 1/3*(VSab-VSca);

VSb = 1/3*(VSbc-VSab);

VSc = 1/3*(VSca-VSbc);

VSalpha = 2/3*(VSa - (0.5*VSb) - (0.5*VSc));

VSbeta = 2/3 *(SQRT3_2*VSb - SQRT3_2*VSc);

VSq = VSalpha*COS_theta + VSbeta*SIN_theta;

VSd = -VSalpha*SIN_theta + VSbeta*COS_theta;

VSd_error = (VSd - VSd_ref);

freq_delta += (Kp_PLL*(VSd_error-AC_FREQ_PERR) + Ki_PLL*VSd_error);

Kp_PLL=0.1

p_VSd_error = VSd_error;

if(freq_delta > 5.) freq_delta = 5.;

if(freq_delta < -5.) freq_delta = -5.;

freq = ((AC_FREQ_NORMAL ? 50 : 60) + freq_delta);

freq_filtered = 0.99*freq_filtered + 0.01*freq;

theta += (PI2*freq_filtered*AC_TSW);

AC_TSW= 0.000033

Lets angle theta goes pi to 2*pi.

My one is very smart, kind of full bridge type but in in put and output it has inductor, first one might work as a filter, but output one is kind a of multilevel or mutually coupled. My be for suppressing ripple current .Lets say my input is 3p 380VAC, 60Hz, Main Transformer MTR runs at 20kHz, DC output should be 50-147 v, charging current 100A. Switching frequency is 120kHz, dead time120. Should have CC and CV mode of operation.

In order to achieve unity power factor control, the phase of the AC voltage needs to be obtained. The phase is obtained through a phase-locked loop (PLL).

Take a look for single phase control structure of the PLL ,

For such similar way I want to mention some of 3-phase equations, could you kindly elaborate it more ?

VSa = 1/3*(VSab-VSca);

VSb = 1/3*(VSbc-VSab);

VSc = 1/3*(VSca-VSbc);

VSalpha = 2/3*(VSa - (0.5*VSb) - (0.5*VSc));

VSbeta = 2/3 *(SQRT3_2*VSb - SQRT3_2*VSc);

VSq = VSalpha*COS_theta + VSbeta*SIN_theta;

VSd = -VSalpha*SIN_theta + VSbeta*COS_theta;

VSd_error = (VSd - VSd_ref);

freq_delta += (Kp_PLL*(VSd_error-AC_FREQ_PERR) + Ki_PLL*VSd_error);

Kp_PLL=0.1

p_VSd_error = VSd_error;

if(freq_delta > 5.) freq_delta = 5.;

if(freq_delta < -5.) freq_delta = -5.;

freq = ((AC_FREQ_NORMAL ? 50 : 60) + freq_delta);

freq_filtered = 0.99*freq_filtered + 0.01*freq;

theta += (PI2*freq_filtered*AC_TSW);

AC_TSW= 0.000033

Lets angle theta goes pi to 2*pi.

My one is very smart, kind of full bridge type but in in put and output it has inductor, first one might work as a filter, but output one is kind a of multilevel or mutually coupled. My be for suppressing ripple current .Lets say my input is 3p 380VAC, 60Hz, Main Transformer MTR runs at 20kHz, DC output should be 50-147 v, charging current 100A. Switching frequency is 120kHz, dead time120. Should have CC and CV mode of operation.