Hjldioyitsi

Member level 1

Hi all,

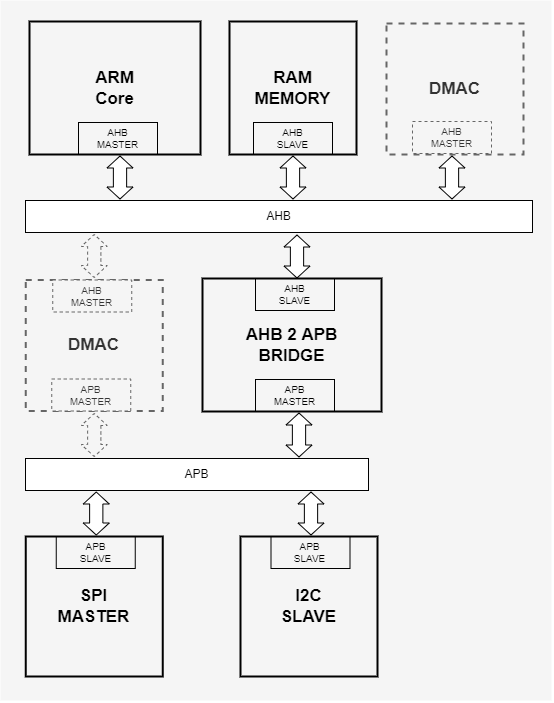

I have seen multiple diagrams of SoCs with DMA Controllers that support different types of AMBA buses, but some put the DMA Controller in between AMBA buses (e.g: AHB and APB, aside to the bus bridge) whilst others put the DMA Controller in the same AMBA bus as the core processor. Are these functionally equivalent? Is one way better than the other? Note that in the example below the DMA Controller has to support access between AHB memory and APB peripherals.

Thanks!

I have seen multiple diagrams of SoCs with DMA Controllers that support different types of AMBA buses, but some put the DMA Controller in between AMBA buses (e.g: AHB and APB, aside to the bus bridge) whilst others put the DMA Controller in the same AMBA bus as the core processor. Are these functionally equivalent? Is one way better than the other? Note that in the example below the DMA Controller has to support access between AHB memory and APB peripherals.

Thanks!