fpmkh0

Newbie level 6

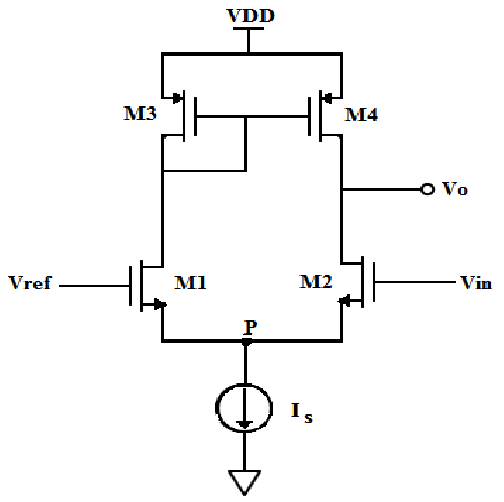

Hi, I want to use differential to single-ended amplifier architecture for the error amplifier in my CMFB loop. I see that in my design, the amplifier does not have a good phase margin. But I haven't seen much information in textbooks about how to compensate for such an amplifier. Razavi warns in his book that such an amplifier might suffer from stability problems due to the mirror pole (compared to a fully differential amplifier), but I could not find in his book talking about compensating for such an amplifier. Can we do something like Miller here? If not, what are the measures I should take to stabilize the amplifier while maintaining its high gain? Thank you.