strahd_von_zarovich

Advanced Member level 4

Hi Everyone,

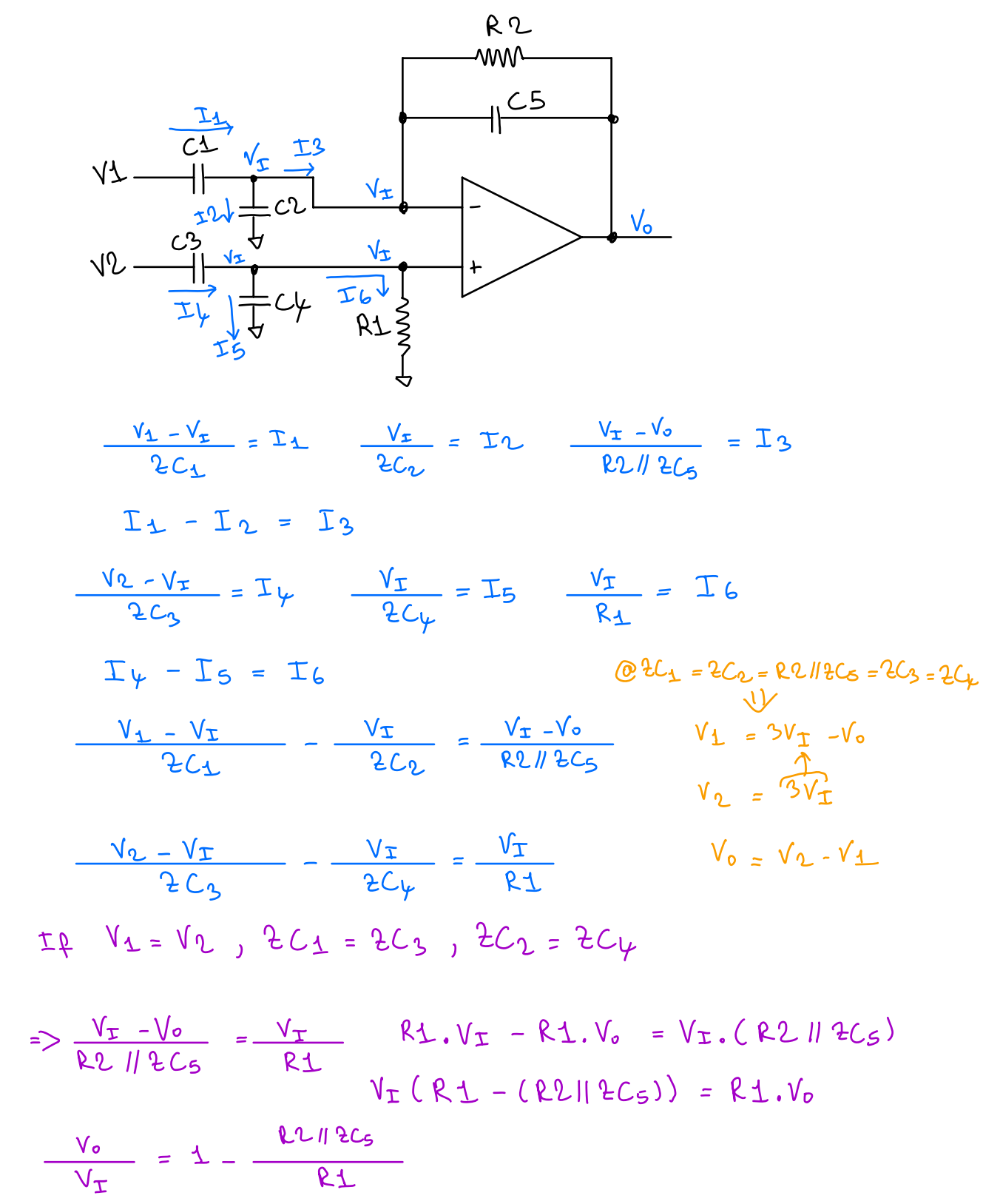

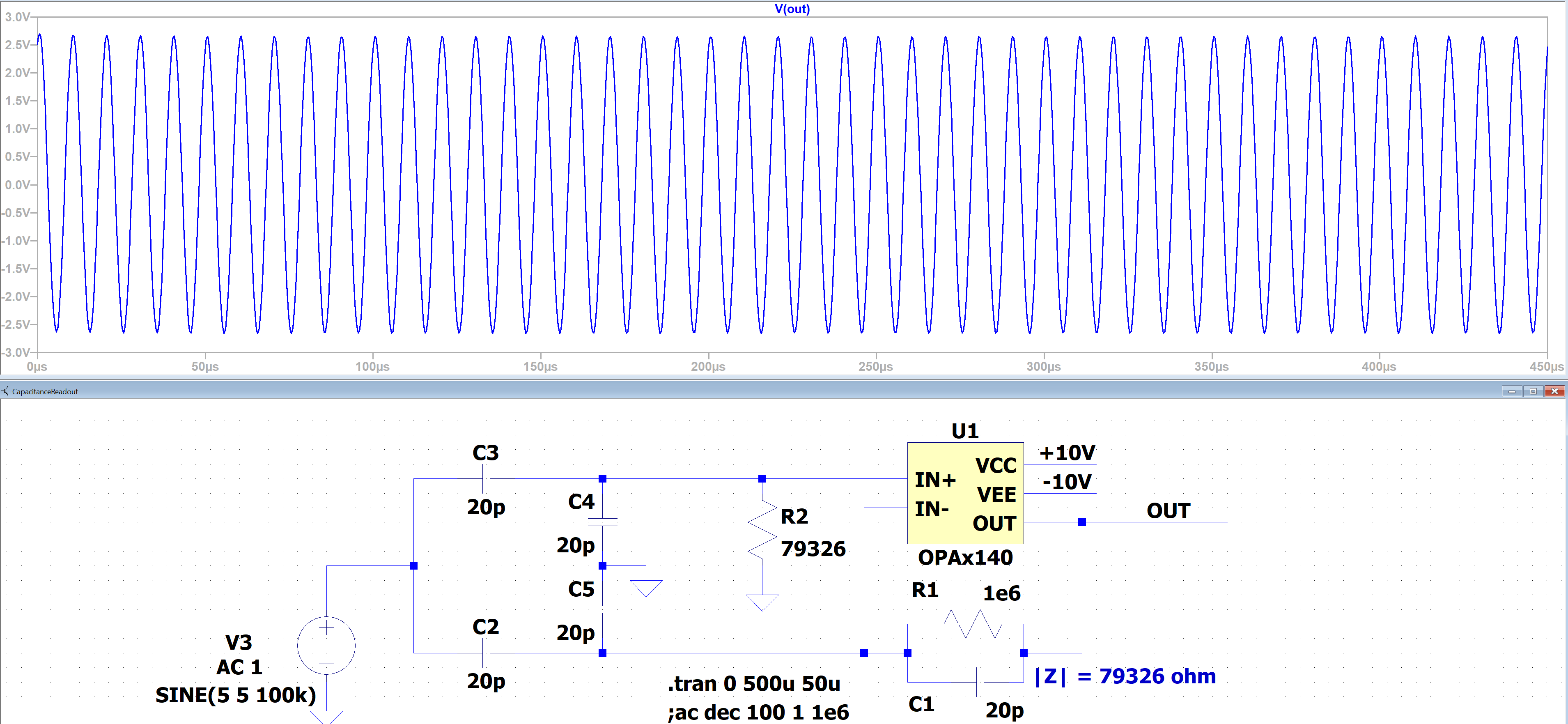

I am trying to understand what did I do wrong. When I set all the capacitors the same value and impedance of R2||C5 to R1 , the output should be V2-V1 and if they are also equal then the output should be zero. However, in LTSpice, I cant get the same result.

I am trying to understand what did I do wrong. When I set all the capacitors the same value and impedance of R2||C5 to R1 , the output should be V2-V1 and if they are also equal then the output should be zero. However, in LTSpice, I cant get the same result.