DNA2683

Advanced Member level 4

Hi Guys,

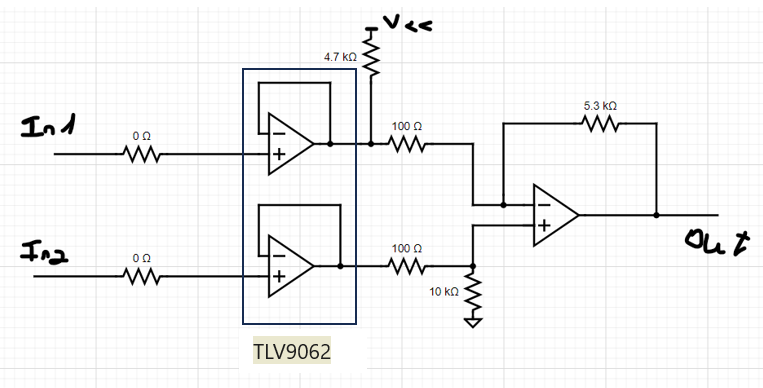

I've been working on a circuit design that involves two input signals passing through buffers before entering a differential op-amp. I'm currently facing an issue with the steady-state behavior of the circuit. When I apply an input of 0V to both of the buffers (or tie both inputs to GND), I expected to see 0V (or perhaps a few millivolts) on both of the buffer outputs. However, for some reason, I'm observing different output voltages from the two buffers.

It's important to note that these buffers are part of the same IC package. I'm puzzled by this behavior, as I expected the outputs to be identical when both inputs are the same.

The buffers I'm using are TI TLV9062. To help you better understand the circuit, I've attached a diagram outlining the concept.

Could anyone provide insights or information on what might be causing this issue? Your assistance in resolving this matter would be greatly appreciated.

I've been working on a circuit design that involves two input signals passing through buffers before entering a differential op-amp. I'm currently facing an issue with the steady-state behavior of the circuit. When I apply an input of 0V to both of the buffers (or tie both inputs to GND), I expected to see 0V (or perhaps a few millivolts) on both of the buffer outputs. However, for some reason, I'm observing different output voltages from the two buffers.

It's important to note that these buffers are part of the same IC package. I'm puzzled by this behavior, as I expected the outputs to be identical when both inputs are the same.

The buffers I'm using are TI TLV9062. To help you better understand the circuit, I've attached a diagram outlining the concept.

Could anyone provide insights or information on what might be causing this issue? Your assistance in resolving this matter would be greatly appreciated.