anila.d90

Newbie

Hello,

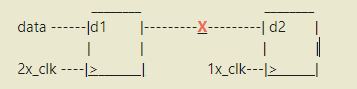

Have a question on if it is possible to detect/create ATPG patterns for At-Speed faults in the path between 2 flops, 1st flop clocked at 2x and 2nd flop clocked at 1x ?

The path is a valid functional path

My assumption is the following will work, but not sure how to write the capture procedure for this:

Say i want to detect a slow-to-rise fault

SHIFT mode : d1 = 0 ; d2 = x (don't care 0/1) ; Shift_clk (same for both flops)

CAPTURE mode :

@launch : d1 = 1 ; pulse 2x_clk ;

@capture : pulse 1x_clk;

Please advice

Have a question on if it is possible to detect/create ATPG patterns for At-Speed faults in the path between 2 flops, 1st flop clocked at 2x and 2nd flop clocked at 1x ?

The path is a valid functional path

My assumption is the following will work, but not sure how to write the capture procedure for this:

Say i want to detect a slow-to-rise fault

SHIFT mode : d1 = 0 ; d2 = x (don't care 0/1) ; Shift_clk (same for both flops)

CAPTURE mode :

@launch : d1 = 1 ; pulse 2x_clk ;

@capture : pulse 1x_clk;

Please advice