Alex_Zhan

Newbie level 6

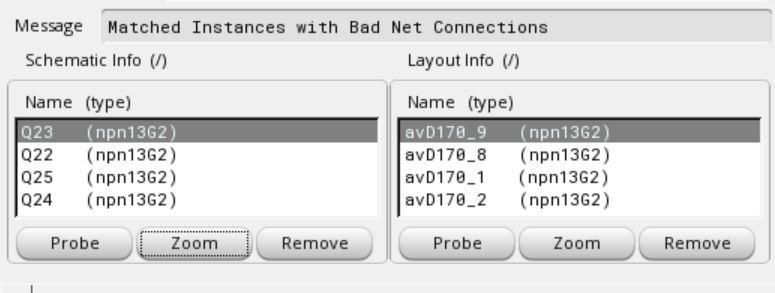

Hello everyone, when I do LVS check in cadence, I find this problem in the picture. This layout can pass the DRC check, and I am sure the devices in the layout are the same as the ones in schematic.

Does anyone know the reason? Thank you deeply!

Does anyone know the reason? Thank you deeply!