Amr Wael

Member level 5

Hello ,

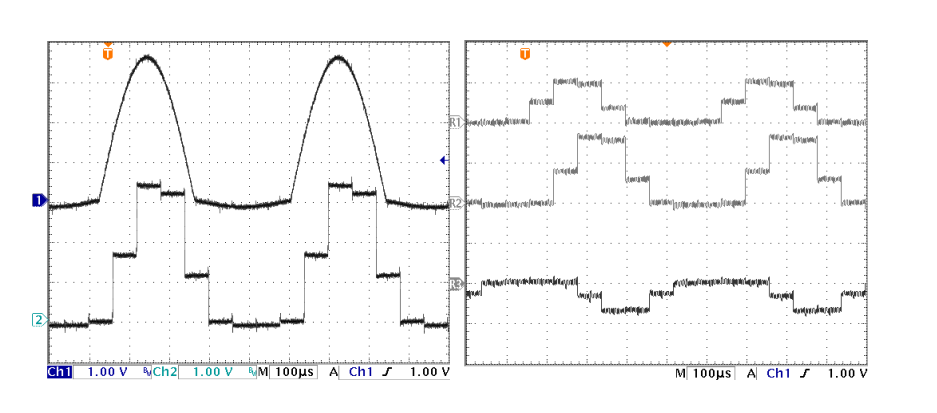

I am trying to implement a module that delays the clock of the sample and hold amplifier by one cycle in order to achieve the signals as in the following photo,

The photo on the left shows a rectified signal and a single sampled signal with a clock.

The photo on the right shows the regular sampled signal with the clock and the other two are sampled signals with delayed clock cycles ( 1 clock cycle for each signal)

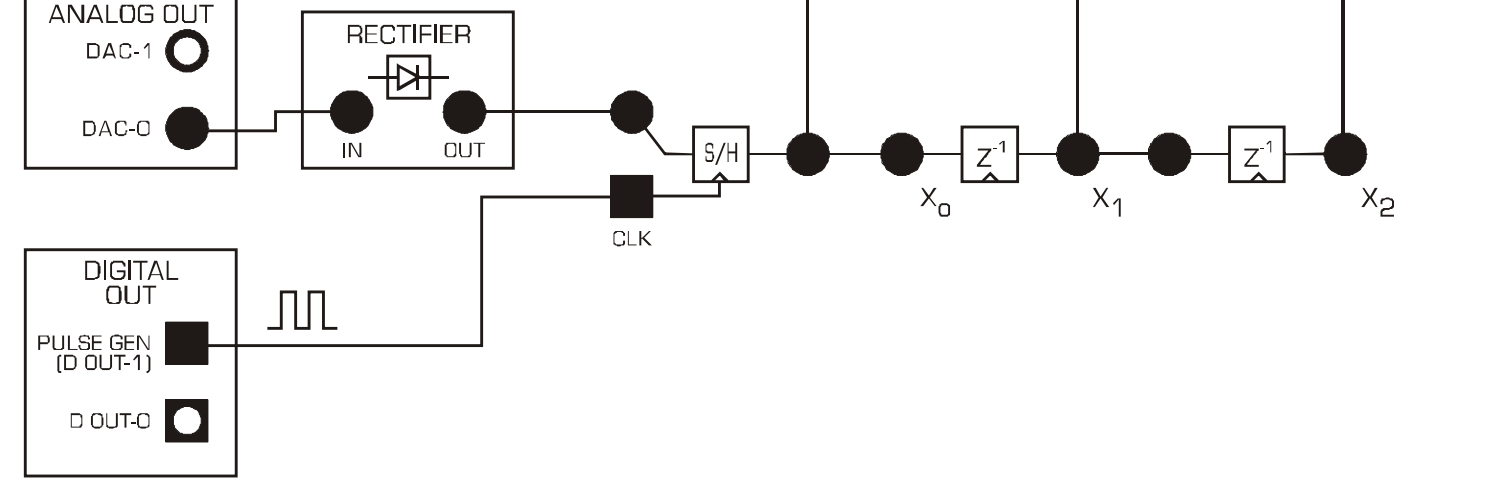

Here is a block diagram for what I am trying to do.

Note : Clock signal is delayed and is also input to Z-1 modules

I Tried using phase shifter based on opamp and RC to delay the clock 360 degrees before the other 2 sample and hold amplifiers but it didn't work.

Any solutions ?????

Thank you very much in advance.

I am trying to implement a module that delays the clock of the sample and hold amplifier by one cycle in order to achieve the signals as in the following photo,

The photo on the left shows a rectified signal and a single sampled signal with a clock.

The photo on the right shows the regular sampled signal with the clock and the other two are sampled signals with delayed clock cycles ( 1 clock cycle for each signal)

Here is a block diagram for what I am trying to do.

Note : Clock signal is delayed and is also input to Z-1 modules

I Tried using phase shifter based on opamp and RC to delay the clock 360 degrees before the other 2 sample and hold amplifiers but it didn't work.

Any solutions ?????

Thank you very much in advance.