Magnethicc

Member level 3

Hi Everyone,

I want to build a circuit which produces shorter and shorter square-wave pulses.

The frequency of the pulse is 62.5kHz and the pulse duration starts from ~100% duty down to ~200ns.

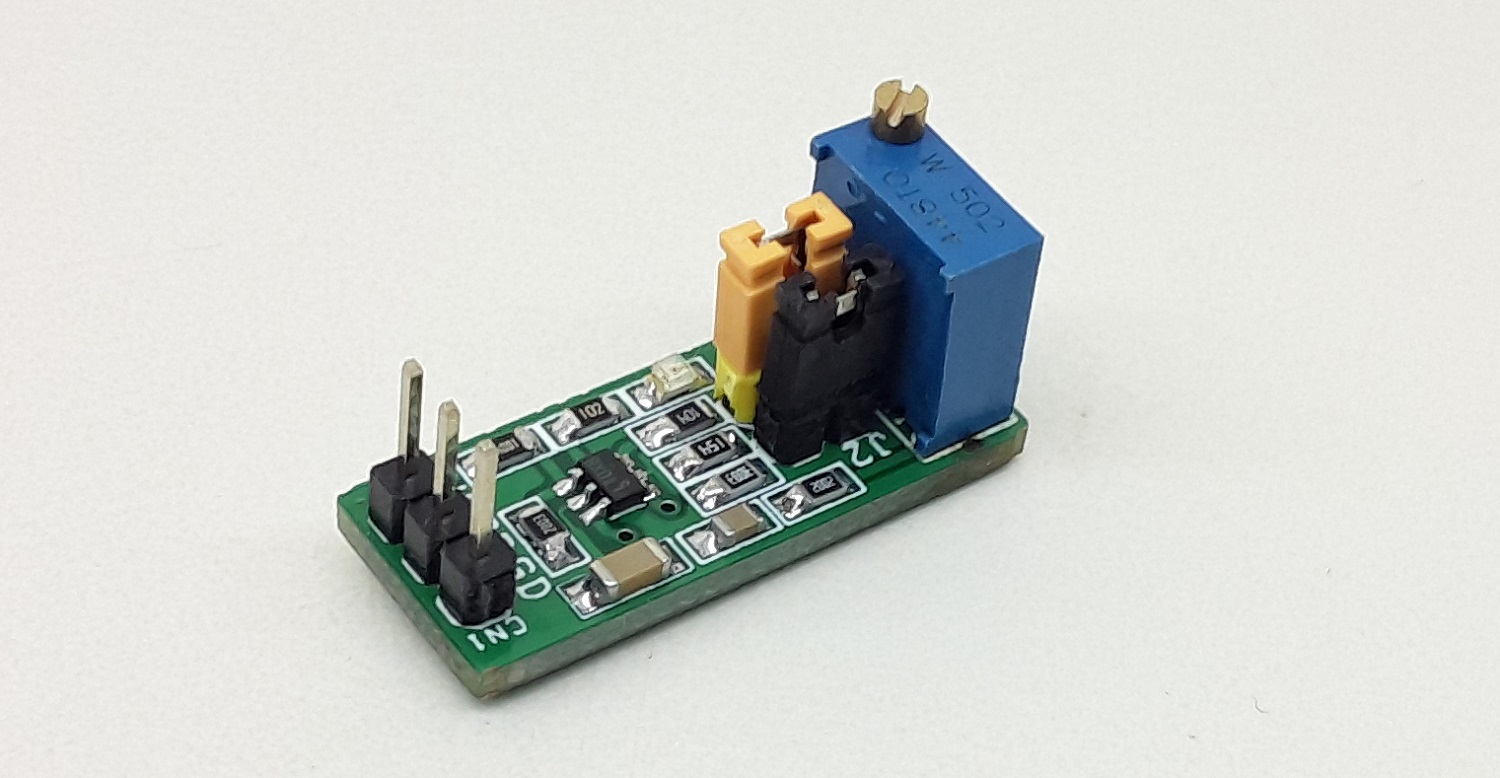

To help with the matter I have a circuit that generates 62.5kHz pulse (25% duty).

Does anyone have any idea on how to realize the circuit?

Thank you.

I want to build a circuit which produces shorter and shorter square-wave pulses.

The frequency of the pulse is 62.5kHz and the pulse duration starts from ~100% duty down to ~200ns.

To help with the matter I have a circuit that generates 62.5kHz pulse (25% duty).

Does anyone have any idea on how to realize the circuit?

Thank you.