Ans5671

Member level 2

Hello all,

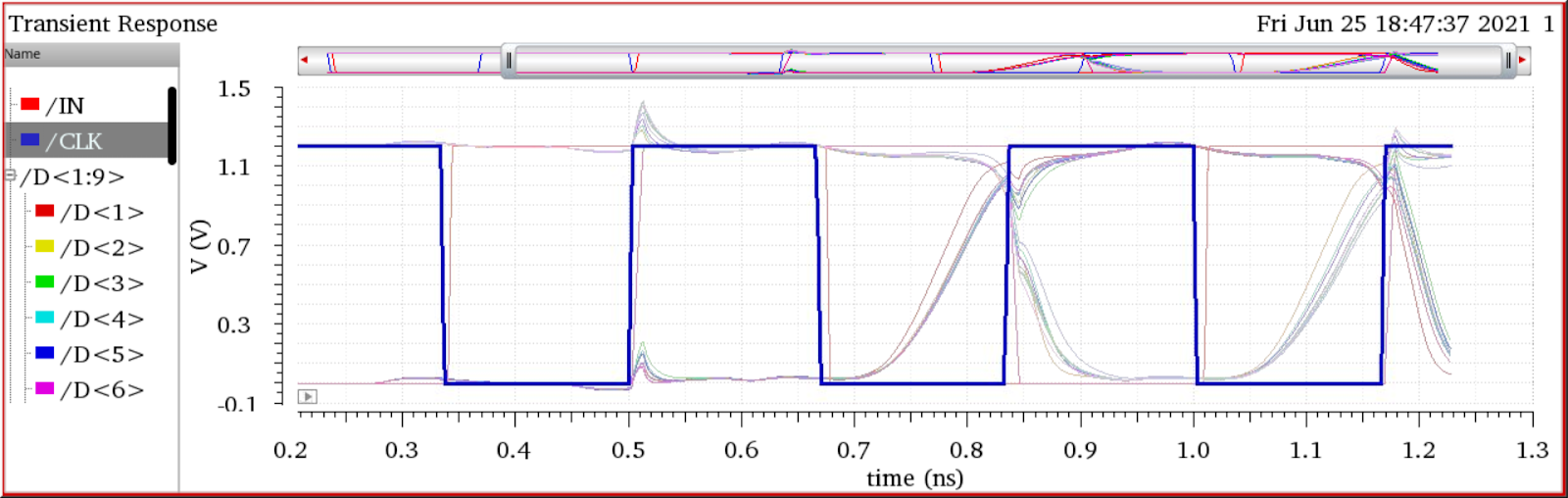

I am designing a 9 bit binary-weighted Nyquist DAC @3GHz. The schematics are ready with good results. I started the layout of the different blocks as Current Source Matrix, Current switches, Current switch drivers. I am not getting good results, mainly because of clock coupling to the driving signals. The clock is routed at M7 and signals on M2 and M3. Can someone help me - I have tried two different floor plans for the switch drivers. Clock - H tree and Mesh.

I am designing a 9 bit binary-weighted Nyquist DAC @3GHz. The schematics are ready with good results. I started the layout of the different blocks as Current Source Matrix, Current switches, Current switch drivers. I am not getting good results, mainly because of clock coupling to the driving signals. The clock is routed at M7 and signals on M2 and M3. Can someone help me - I have tried two different floor plans for the switch drivers. Clock - H tree and Mesh.