goatmxj666

Member level 3

Hello.

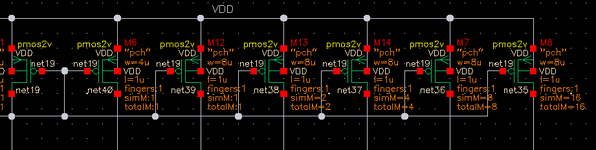

I am currently doing the current mirror layout.

The sizes of each are as follows.

I would like to layout with interdigitation method for matching. I think common centroid layout is not possible as it is too time consuming.

Also, I made some of the mosfets 8um because it was too long to do all the mosfets in 4um.

I was thinking of doing something like "D D D D D D D D D D D D D D C C C C C B B A F E G A B B C C C C C D D D D D D D D D D D D D", is that okay?

I really need some advice from layout experts.

Any advice would be greatly appreciated.

Thanks.

I am currently doing the current mirror layout.

The sizes of each are as follows.

I would like to layout with interdigitation method for matching. I think common centroid layout is not possible as it is too time consuming.

Also, I made some of the mosfets 8um because it was too long to do all the mosfets in 4um.

I was thinking of doing something like "D D D D D D D D D D D D D D C C C C C B B A F E G A B B C C C C C D D D D D D D D D D D D D", is that okay?

I really need some advice from layout experts.

Any advice would be greatly appreciated.

Thanks.