flyline19

Newbie level 5

Hello, I have a Nexys a7 100 board and I want to use the VGA port. I haven't used the VGA port before, and I haven't been able to find any literature on how to configure my constraint file. This is a LOT of text imo, so I'd just skip to my constraint file down there. I only need help with that piece (the constraint file) as I'm pretty sure the rest works fine. I provided the rest in case someone thinks that it's something else.

Here is my VGA_sync file that I followed from a text book:

####################################################################################

####################################################################################

####################################################################################

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity vga_sync is

Port ( --INPUTS

clk : in STD_LOGIC;

rst : in STD_LOGIC;

--OUTPUTS

hsync : out STD_LOGIC;

vsync : out STD_LOGIC;

video_on : out STD_LOGIC;

p_tick : out STD_LOGIC;

pixel_x : out STD_LOGIC_VECTOR (9 downto 0);

pixel_y : out STD_LOGIC_VECTOR (9 downto 0));

end vga_sync;

architecture Behavioral of vga_sync is

--##############################################

--VGA 640 - by - 480 sync parameters

--HORIZONTAL COMPONENTS

constant HD : integer := 640; --Display Area

constant HF : integer := 16; --Front Porch

constant HB : integer := 48; --Back Porch

constant HR : integer := 96; --Horizontal Retrace

--VERTICAL COMPONENTS

constant VD : integer := 480; --Display Area

constant VF : integer := 10; --Front Porch

constant VB : integer := 33; -- ack Porch

constant VR : integer := 2; --Vertical Retrace

--##############################################

-- Mod-2 counter

signal mod2_reg, mod2_next : STD_LOGIC;

--##############################################

--Sync counters

--Horizontal Counter

signal h_count_reg, h_count_next : UNSIGNED (9 downto 0);

--Vertical Counter

signal v_count_reg, v_count_next : UNSIGNED (9 downto 0);

--##############################################

--Output Buffer

--Horizontal

signal h_sync_reg, h_sync_next : STD_LOGIC;

--Vertical

signal v_sync_reg, v_sync_next : STD_LOGIC;

--##############################################

--Status Signal

signal h_end, v_end, pixel_tick : STD_LOGIC;

begin

--##############################################

--Clock Process

process(clk, rst)

begin

if (rst = '1') then

mod2_reg <= '0';

v_count_reg <= (others => '0');

h_count_reg <= (others => '0');

v_sync_reg <= '0';

h_sync_reg <= '0';

elsif (clk'event and clk = '1') then

mod2_reg <= mod2_next;

v_count_reg <= v_count_next;

h_count_reg <= h_count_next;

v_sync_reg <= v_sync_next;

h_sync_reg <= h_sync_next;

end if;

end process;

--##############################################

-- Mod - 2 circuit to generate 25 MHz enable tick

mod2_next <= not mod2_reg;

-- 25 MHz pixel tick

pixel_tick <= '1' when mod2_reg = '1' else '0';

--Status

--End of Horiz. counter

h_end <= '1' when h_count_reg = (HD + HF + HB + HR -1) else

'0';

--End of Vert. counter

v_end <= '1' when v_count_reg = (VD + VF + VB + VR -1) else

'0';

--Mod-800 Horz. sync counter

process (h_count_reg, h_end, pixel_tick)

begin

if (pixel_tick = '1') then --25 MHz tick

if h_end = '1' then --End of the horizontal scan

h_count_next <= (others => '0'); --Resetting the Horiz. scan

else

h_count_next <= h_count_reg + 1; --Increment the scan

end if;

else

h_count_next <= h_count_reg; --Not a clk cycle that is part of the 25 MHz cycle, i.e. do nothing to Horiz.

end if;

end process;

--Mod-525 Vert. sync counter

process (v_count_reg, v_end, h_end, pixel_tick)

begin

if (pixel_tick = '1') and (h_end = '1') then

if (v_end = '1') then

v_count_next <= (others => '0');

else

v_count_next <= v_count_reg + 1;

end if;

else

v_count_next <= v_count_reg;

end if;

end process;

--##############################################

--Horiz. and Vert. sync buffered to avoid glitch

--The sync signal will be sent when then scan is in the middle of the retrace

h_sync_next <= '1' when (h_count_reg >= (HD + HF) and h_count_reg <= (HD + HF + HR -1)) else

'0';

v_sync_next <= '1' when (v_count_reg >= (VD + VF) and v_count_reg <= (VD + VF + VR -1)) else

'0';

--##############################################

--Video on/off

video_on <= '1' when (h_count_reg < HD and v_count_reg < VD) else

'0';

--##############################################

--Output Signal

hsync <= h_sync_reg;

vsync <= v_sync_reg;

pixel_x <= STD_LOGIC_VECTOR(h_count_reg);

pixel_y <= STD_LOGIC_VECTOR(v_count_reg);

p_tick <= pixel_tick;

end Behavioral;

##########################################################################################

This ^^^ I am pretty sure works. And here (below this) is my test ckt:

##########################################################################################

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity vga_test is

Port ( --INPUTS

clk : in STD_LOGIC;

rst : in STD_LOGIC;

SW : in STD_LOGIC_VECTOR (2 downto 0);

--OUTPUTS

hsync : out STD_LOGIC;

vsync : out STD_LOGIC;

rgb : out STD_LOGIC_VECTOR (2 downto 0));

end vga_test;

architecture Behavioral of vga_test is

signal rgb_reg : STD_LOGIC_VECTOR (2 downto 0);

signal video_on : STD_LOGIC;

begin

--Instantiate a VGA_sync

vga_sync_unit : entity work.vga_sync

port map( --INPUTS

clk => clk,

rst => rst,

--OUTPUTS

hsync => hsync,

vsync => vsync,

video_on => video_on,

p_tick => open,

pixel_x => open,

pixel_y => open);

--RGB buffer

process (clk, rst)

begin

if (rst = '1') then

rgb_reg <= (others => '0');

elsif (clk'event and clk = '1') then

rgb_reg <= SW;

end if;

end process;

--Setting the output

rgb <= rgb_reg when video_on = '1' else

"000";

end Behavioral;

##########################################################################################

This ^^^ I am pretty sure works as well. And here (below this) is my constraint file ckt:

##########################################################################################

CONSTRAINT FILE BELOW

##########################################################################################

# Clock signal

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L12P_T1_MRCC_35 Sch=clk100mhz

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clk}];

#Button

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports { rst }]; #IO_L9P_T1_DQS_14 Sch=btnc

#Switches

set_property -dict { PACKAGE_PIN J15 IOSTANDARD LVCMOS33 } [get_ports { SW[0] }]; #IO_L24N_T3_RS0_15 Sch=sw[0]

set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports { SW[1] }]; #IO_L3N_T0_DQS_EMCCLK_14 Sch=sw[1]

set_property -dict { PACKAGE_PIN M13 IOSTANDARD LVCMOS33 } [get_ports { SW[2] }]; #IO_L6N_T0_D08_VREF_14 Sch=sw[2]

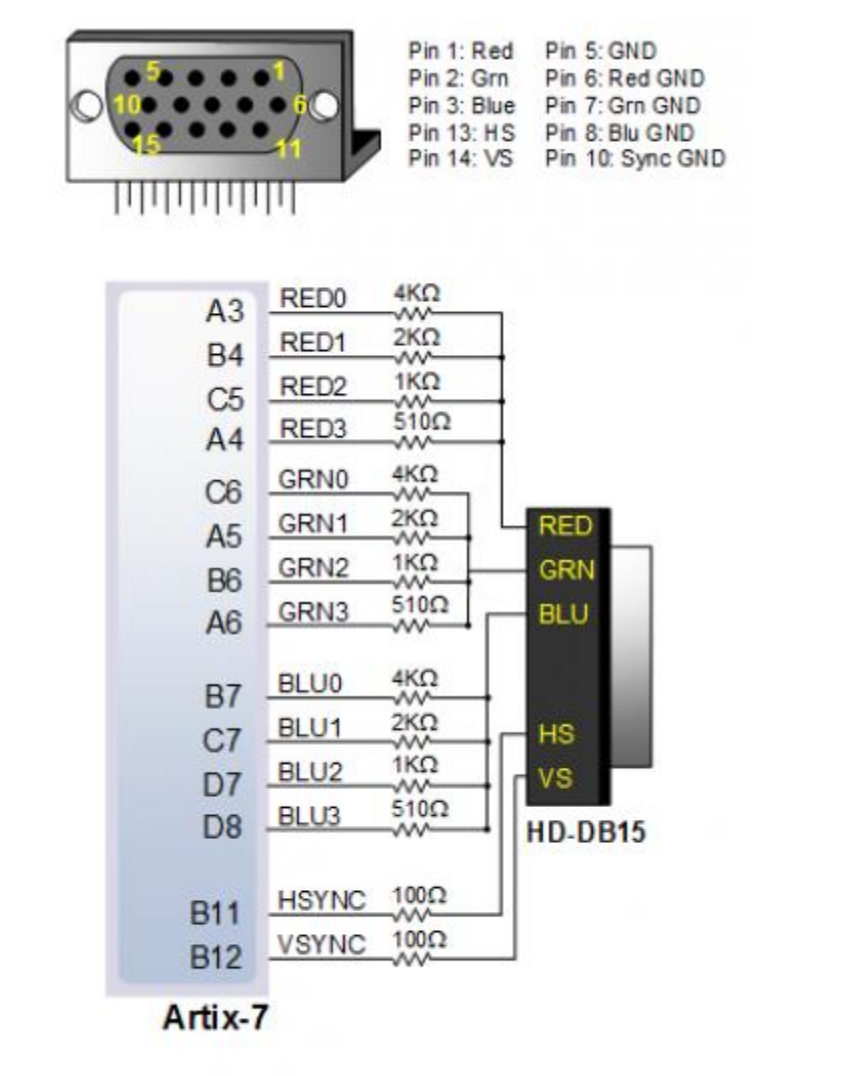

#VGA Connector --personal note -- USE ONE OF EACH R, G, and B. NOT ALL???

#set_property -dict { PACKAGE_PIN A3 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L8N_T1_AD14N_35 Sch=vga_r[0]

#set_property -dict { PACKAGE_PIN B4 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L7N_T1_AD6N_35 Sch=vga_r[1]

#set_property -dict { PACKAGE_PIN C5 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L1N_T0_AD4N_35 Sch=vga_r[2]

set_property -dict { PACKAGE_PIN A4 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L8P_T1_AD14P_35 Sch=vga_r[3]

#set_property -dict { PACKAGE_PIN C6 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L1P_T0_AD4P_35 Sch=vga_g[0]

#set_property -dict { PACKAGE_PIN A5 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L3N_T0_DQS_AD5N_35 Sch=vga_g[1]

#set_property -dict { PACKAGE_PIN B6 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L2N_T0_AD12N_35 Sch=vga_g[2]

set_property -dict { PACKAGE_PIN A6 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L3P_T0_DQS_AD5P_35 Sch=vga_g[3]

#set_property -dict { PACKAGE_PIN B7 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L2P_T0_AD12P_35 Sch=vga_b[0]

#set_property -dict { PACKAGE_PIN C7 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L4N_T0_35 Sch=vga_b[1]

#set_property -dict { PACKAGE_PIN D7 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L6N_T0_VREF_35 Sch=vga_b[2]

set_property -dict { PACKAGE_PIN D8 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L4P_T0_35 Sch=vga_b[3]

set_property -dict { PACKAGE_PIN B11 IOSTANDARD LVCMOS33 } [get_ports { hsync }]; #IO_L4P_T0_15 Sch=vga_hs

set_property -dict { PACKAGE_PIN B12 IOSTANDARD LVCMOS33 } [get_ports { vsync }]; #IO_L3N_T0_DQS_AD1N_15 Sch=vga_vs

##########################################################################################

This ^^^ is what I have issues with (I think). and below is from the ref manual for the board:

##########################################################################################

Follow up... I think that it has to do with my monitor being 1280 x 1040. I'm trying to find the specs on its front proch, BP, and retrace ....

Here is my VGA_sync file that I followed from a text book:

####################################################################################

####################################################################################

####################################################################################

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity vga_sync is

Port ( --INPUTS

clk : in STD_LOGIC;

rst : in STD_LOGIC;

--OUTPUTS

hsync : out STD_LOGIC;

vsync : out STD_LOGIC;

video_on : out STD_LOGIC;

p_tick : out STD_LOGIC;

pixel_x : out STD_LOGIC_VECTOR (9 downto 0);

pixel_y : out STD_LOGIC_VECTOR (9 downto 0));

end vga_sync;

architecture Behavioral of vga_sync is

--##############################################

--VGA 640 - by - 480 sync parameters

--HORIZONTAL COMPONENTS

constant HD : integer := 640; --Display Area

constant HF : integer := 16; --Front Porch

constant HB : integer := 48; --Back Porch

constant HR : integer := 96; --Horizontal Retrace

--VERTICAL COMPONENTS

constant VD : integer := 480; --Display Area

constant VF : integer := 10; --Front Porch

constant VB : integer := 33; -- ack Porch

constant VR : integer := 2; --Vertical Retrace

--##############################################

-- Mod-2 counter

signal mod2_reg, mod2_next : STD_LOGIC;

--##############################################

--Sync counters

--Horizontal Counter

signal h_count_reg, h_count_next : UNSIGNED (9 downto 0);

--Vertical Counter

signal v_count_reg, v_count_next : UNSIGNED (9 downto 0);

--##############################################

--Output Buffer

--Horizontal

signal h_sync_reg, h_sync_next : STD_LOGIC;

--Vertical

signal v_sync_reg, v_sync_next : STD_LOGIC;

--##############################################

--Status Signal

signal h_end, v_end, pixel_tick : STD_LOGIC;

begin

--##############################################

--Clock Process

process(clk, rst)

begin

if (rst = '1') then

mod2_reg <= '0';

v_count_reg <= (others => '0');

h_count_reg <= (others => '0');

v_sync_reg <= '0';

h_sync_reg <= '0';

elsif (clk'event and clk = '1') then

mod2_reg <= mod2_next;

v_count_reg <= v_count_next;

h_count_reg <= h_count_next;

v_sync_reg <= v_sync_next;

h_sync_reg <= h_sync_next;

end if;

end process;

--##############################################

-- Mod - 2 circuit to generate 25 MHz enable tick

mod2_next <= not mod2_reg;

-- 25 MHz pixel tick

pixel_tick <= '1' when mod2_reg = '1' else '0';

--Status

--End of Horiz. counter

h_end <= '1' when h_count_reg = (HD + HF + HB + HR -1) else

'0';

--End of Vert. counter

v_end <= '1' when v_count_reg = (VD + VF + VB + VR -1) else

'0';

--Mod-800 Horz. sync counter

process (h_count_reg, h_end, pixel_tick)

begin

if (pixel_tick = '1') then --25 MHz tick

if h_end = '1' then --End of the horizontal scan

h_count_next <= (others => '0'); --Resetting the Horiz. scan

else

h_count_next <= h_count_reg + 1; --Increment the scan

end if;

else

h_count_next <= h_count_reg; --Not a clk cycle that is part of the 25 MHz cycle, i.e. do nothing to Horiz.

end if;

end process;

--Mod-525 Vert. sync counter

process (v_count_reg, v_end, h_end, pixel_tick)

begin

if (pixel_tick = '1') and (h_end = '1') then

if (v_end = '1') then

v_count_next <= (others => '0');

else

v_count_next <= v_count_reg + 1;

end if;

else

v_count_next <= v_count_reg;

end if;

end process;

--##############################################

--Horiz. and Vert. sync buffered to avoid glitch

--The sync signal will be sent when then scan is in the middle of the retrace

h_sync_next <= '1' when (h_count_reg >= (HD + HF) and h_count_reg <= (HD + HF + HR -1)) else

'0';

v_sync_next <= '1' when (v_count_reg >= (VD + VF) and v_count_reg <= (VD + VF + VR -1)) else

'0';

--##############################################

--Video on/off

video_on <= '1' when (h_count_reg < HD and v_count_reg < VD) else

'0';

--##############################################

--Output Signal

hsync <= h_sync_reg;

vsync <= v_sync_reg;

pixel_x <= STD_LOGIC_VECTOR(h_count_reg);

pixel_y <= STD_LOGIC_VECTOR(v_count_reg);

p_tick <= pixel_tick;

end Behavioral;

##########################################################################################

This ^^^ I am pretty sure works. And here (below this) is my test ckt:

##########################################################################################

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity vga_test is

Port ( --INPUTS

clk : in STD_LOGIC;

rst : in STD_LOGIC;

SW : in STD_LOGIC_VECTOR (2 downto 0);

--OUTPUTS

hsync : out STD_LOGIC;

vsync : out STD_LOGIC;

rgb : out STD_LOGIC_VECTOR (2 downto 0));

end vga_test;

architecture Behavioral of vga_test is

signal rgb_reg : STD_LOGIC_VECTOR (2 downto 0);

signal video_on : STD_LOGIC;

begin

--Instantiate a VGA_sync

vga_sync_unit : entity work.vga_sync

port map( --INPUTS

clk => clk,

rst => rst,

--OUTPUTS

hsync => hsync,

vsync => vsync,

video_on => video_on,

p_tick => open,

pixel_x => open,

pixel_y => open);

--RGB buffer

process (clk, rst)

begin

if (rst = '1') then

rgb_reg <= (others => '0');

elsif (clk'event and clk = '1') then

rgb_reg <= SW;

end if;

end process;

--Setting the output

rgb <= rgb_reg when video_on = '1' else

"000";

end Behavioral;

##########################################################################################

This ^^^ I am pretty sure works as well. And here (below this) is my constraint file ckt:

##########################################################################################

CONSTRAINT FILE BELOW

##########################################################################################

# Clock signal

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L12P_T1_MRCC_35 Sch=clk100mhz

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clk}];

#Button

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports { rst }]; #IO_L9P_T1_DQS_14 Sch=btnc

#Switches

set_property -dict { PACKAGE_PIN J15 IOSTANDARD LVCMOS33 } [get_ports { SW[0] }]; #IO_L24N_T3_RS0_15 Sch=sw[0]

set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports { SW[1] }]; #IO_L3N_T0_DQS_EMCCLK_14 Sch=sw[1]

set_property -dict { PACKAGE_PIN M13 IOSTANDARD LVCMOS33 } [get_ports { SW[2] }]; #IO_L6N_T0_D08_VREF_14 Sch=sw[2]

#VGA Connector --personal note -- USE ONE OF EACH R, G, and B. NOT ALL???

#set_property -dict { PACKAGE_PIN A3 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L8N_T1_AD14N_35 Sch=vga_r[0]

#set_property -dict { PACKAGE_PIN B4 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L7N_T1_AD6N_35 Sch=vga_r[1]

#set_property -dict { PACKAGE_PIN C5 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L1N_T0_AD4N_35 Sch=vga_r[2]

set_property -dict { PACKAGE_PIN A4 IOSTANDARD LVCMOS33 } [get_ports { rgb[2] }]; #IO_L8P_T1_AD14P_35 Sch=vga_r[3]

#set_property -dict { PACKAGE_PIN C6 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L1P_T0_AD4P_35 Sch=vga_g[0]

#set_property -dict { PACKAGE_PIN A5 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L3N_T0_DQS_AD5N_35 Sch=vga_g[1]

#set_property -dict { PACKAGE_PIN B6 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L2N_T0_AD12N_35 Sch=vga_g[2]

set_property -dict { PACKAGE_PIN A6 IOSTANDARD LVCMOS33 } [get_ports { rgb[1] }]; #IO_L3P_T0_DQS_AD5P_35 Sch=vga_g[3]

#set_property -dict { PACKAGE_PIN B7 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L2P_T0_AD12P_35 Sch=vga_b[0]

#set_property -dict { PACKAGE_PIN C7 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L4N_T0_35 Sch=vga_b[1]

#set_property -dict { PACKAGE_PIN D7 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L6N_T0_VREF_35 Sch=vga_b[2]

set_property -dict { PACKAGE_PIN D8 IOSTANDARD LVCMOS33 } [get_ports { rgb[0] }]; #IO_L4P_T0_35 Sch=vga_b[3]

set_property -dict { PACKAGE_PIN B11 IOSTANDARD LVCMOS33 } [get_ports { hsync }]; #IO_L4P_T0_15 Sch=vga_hs

set_property -dict { PACKAGE_PIN B12 IOSTANDARD LVCMOS33 } [get_ports { vsync }]; #IO_L3N_T0_DQS_AD1N_15 Sch=vga_vs

##########################################################################################

This ^^^ is what I have issues with (I think). and below is from the ref manual for the board:

##########################################################################################

--- Updated ---

Follow up... I think that it has to do with my monitor being 1280 x 1040. I'm trying to find the specs on its front proch, BP, and retrace ....

Last edited: