skyworld_cy

Junior Member level 3

Hi,

I'm new to conformal lec and confused by some results.

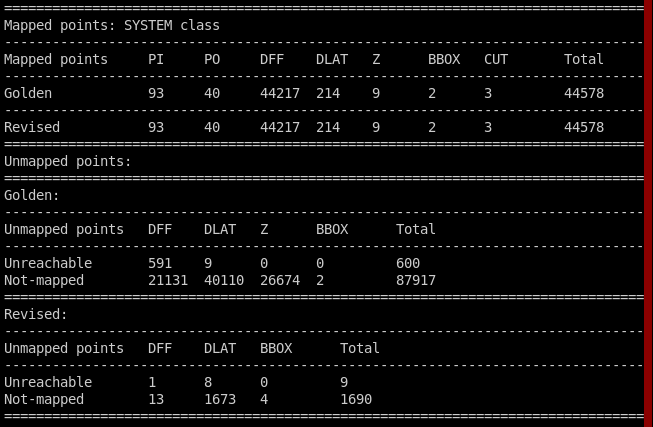

as figure shows a RTL compared to synthesis netlist:

the golden has not-mapped DFF as 21131 while netlist has only 13 DFF not mapped. Does this mean the RTL has so many redundant logic to be optimized by synthesis tool? thanks.

I'm new to conformal lec and confused by some results.

as figure shows a RTL compared to synthesis netlist:

the golden has not-mapped DFF as 21131 while netlist has only 13 DFF not mapped. Does this mean the RTL has so many redundant logic to be optimized by synthesis tool? thanks.