Sameerpy

Newbie level 5

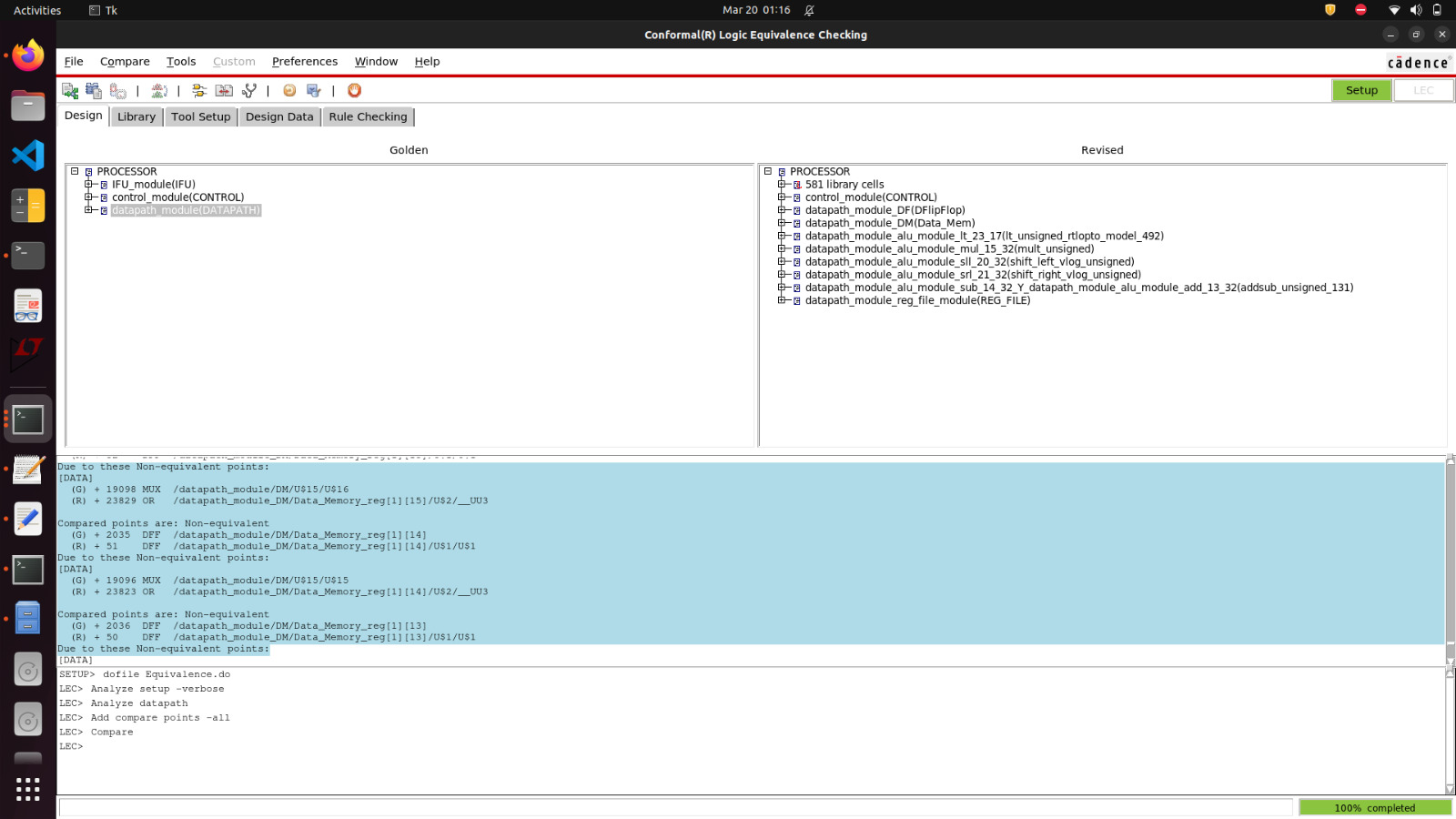

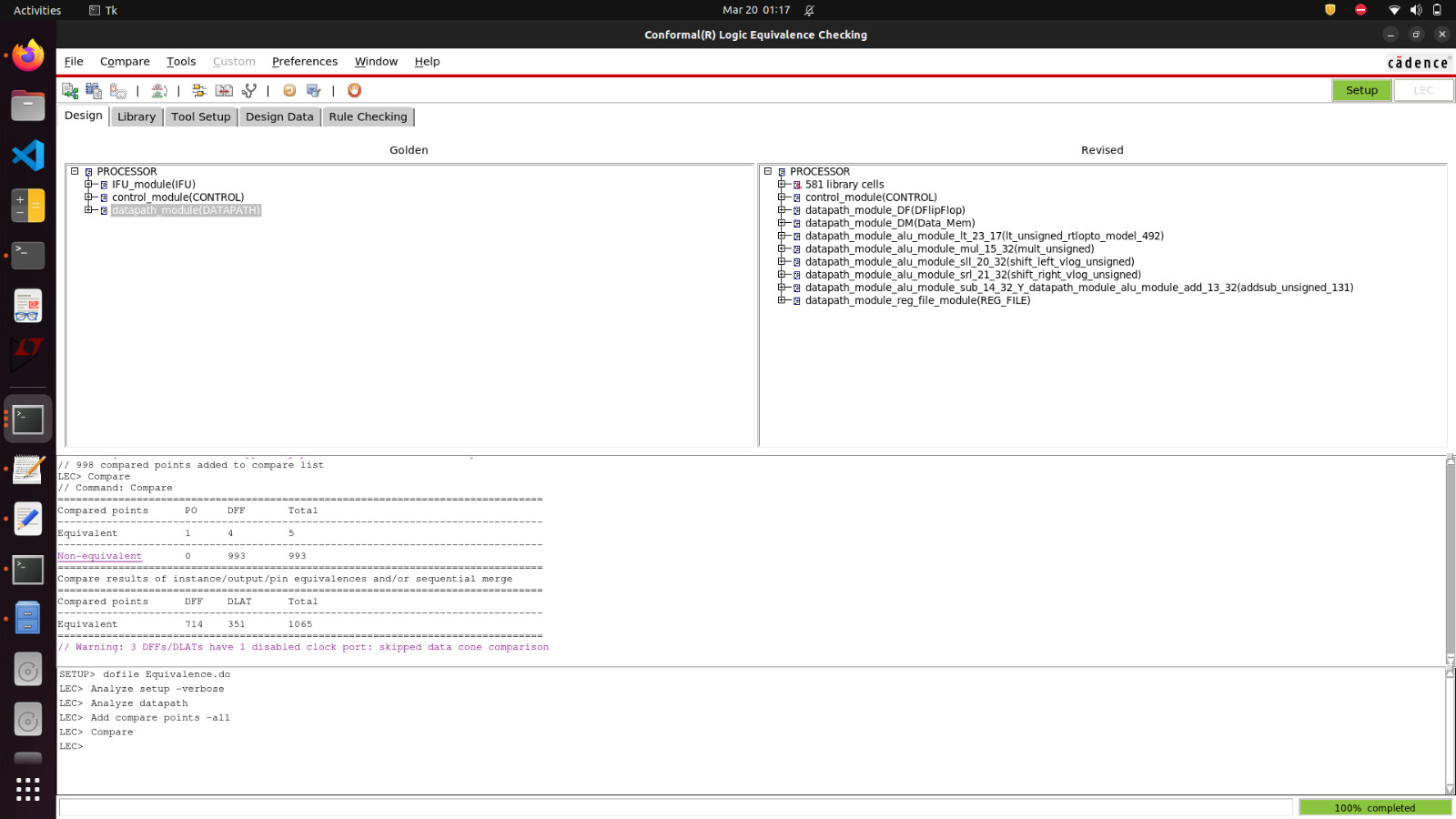

WHEN I COMPARING MY GOLDEN.V WITH revised netlist during conformal , I got these non-equivalent point for every reg memory and for every data memory. I don't know what to do with these non-equivalent point. I've been stuck here for the past four days. Please help me in this and how can I remove this non- equivalent point , since I am new to this I really don't know what to do.