Eugen_E

Full Member level 6

Hello,

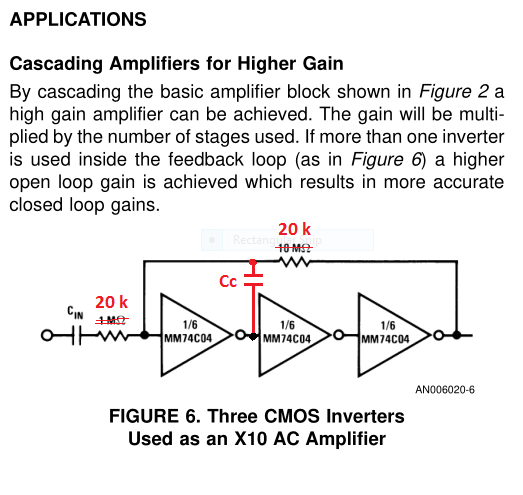

I've tried to use in a circuit this improved (high gain, 3 gates) 4069 amplifier from the old AN-88 (National Semiconductor),

instead of a better amplifier, because I had unused gates available.

This is used at very low frequency and DC, so low bandwidth is not a problem.

I built the circuit with 20 k resistors (values in red), VDD=5 V, and it oscillates at about 2.4 MHz.

Then I tried to compensate the amplifier by adding Cc:

Should I use a proper opamp amplifier?

Thanks

I've tried to use in a circuit this improved (high gain, 3 gates) 4069 amplifier from the old AN-88 (National Semiconductor),

instead of a better amplifier, because I had unused gates available.

This is used at very low frequency and DC, so low bandwidth is not a problem.

I built the circuit with 20 k resistors (values in red), VDD=5 V, and it oscillates at about 2.4 MHz.

Then I tried to compensate the amplifier by adding Cc:

- for Cc = 22 nF, it oscillates at about 38 kHz

- for Cc = 100 nF, it oscillates at about 9.8 kHz.

Should I use a proper opamp amplifier?

Thanks

Last edited: