akbarza

Full Member level 2

hi

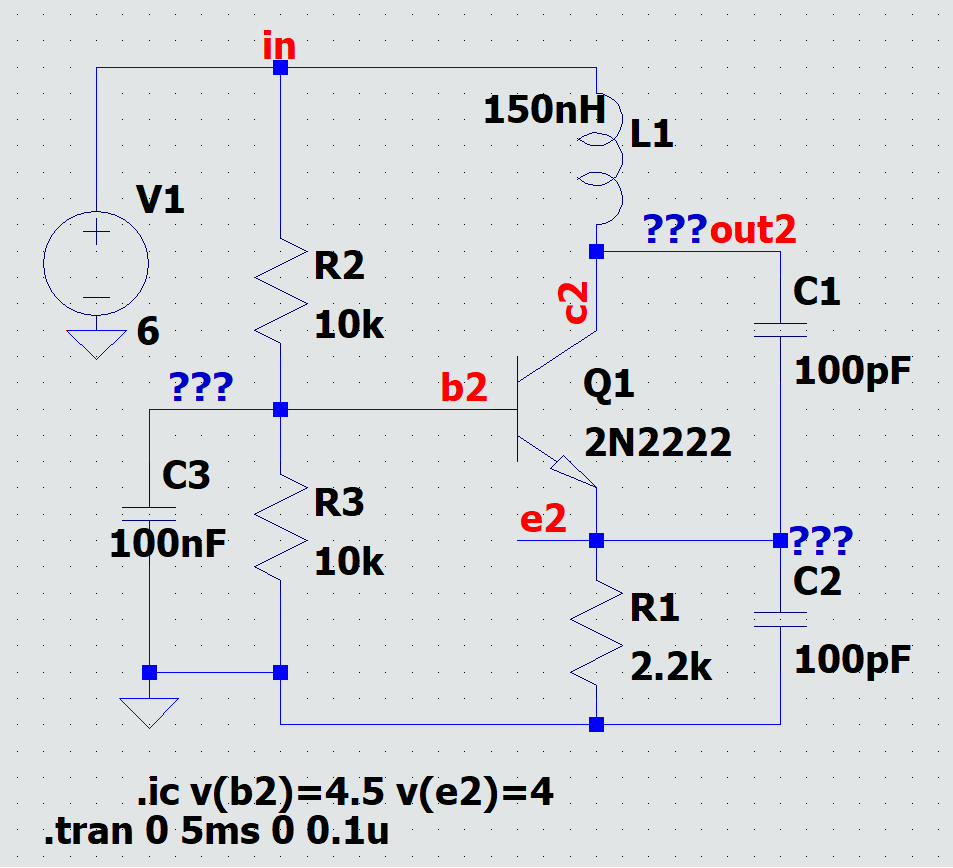

schematic:

I have written about this schematic in https://groups.io/g/LTspice/topic/102947920#150070 , and I take some explanation from that ltspice group members, but I want to know more explanation about it.

note: the schematic and .asc file is related to ltspice(I run it in ltspice)

I uploaded a file as colpits_osc3.zip that contains colpits_osc3.asc and colpits_osc3.plt and a pic of this plt file.

as I know for a bjt transistor when v_be is approximately larger than 0.6 then the transistor is on and there will be a current from collector to emitter and if v_be<0.6( approximately) then it is off and there is no current from collector to emitter.

but as you can see in the plt file or its pic, for v(b2)-v(e2)<0.6 there is current, and also the pick of current occurred in v(b2)-v(e2)<0.6.

is it true?plz, explain

can explain to me about positive feedback that is needed for oscillation in this circuit.

if i delete c3, the circuit oscilate?

can explain to me, how the value of capacitors and resistors were chosen?

thanks

schematic:

I have written about this schematic in https://groups.io/g/LTspice/topic/102947920#150070 , and I take some explanation from that ltspice group members, but I want to know more explanation about it.

note: the schematic and .asc file is related to ltspice(I run it in ltspice)

I uploaded a file as colpits_osc3.zip that contains colpits_osc3.asc and colpits_osc3.plt and a pic of this plt file.

as I know for a bjt transistor when v_be is approximately larger than 0.6 then the transistor is on and there will be a current from collector to emitter and if v_be<0.6( approximately) then it is off and there is no current from collector to emitter.

but as you can see in the plt file or its pic, for v(b2)-v(e2)<0.6 there is current, and also the pick of current occurred in v(b2)-v(e2)<0.6.

is it true?plz, explain

can explain to me about positive feedback that is needed for oscillation in this circuit.

if i delete c3, the circuit oscilate?

can explain to me, how the value of capacitors and resistors were chosen?

thanks