imrankhanPNU

Member level 1

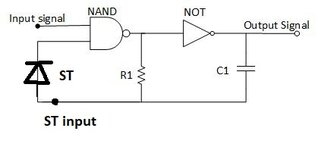

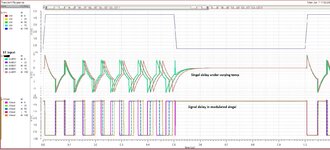

I am doing PVT analysis of an RC-based multi-vibrator. Simulations under varying temperature (0-100 C) and process corners (FF, FS, SF, SS) show signal delay in the modulated signals. This delay is due to the effect of temp and process on R1, C1, and MOSFET's threshold voltage.

-I used PVT independent Schmitt trigger (ST) with fully adjustable threshold voltage to mitigate the modulated signal delay, but the ST does not work in delay mitigation.

Please comment: Is PVT-independent ST a wise choice to mitigate signal delay? How can o get PVT-independent modulated signal?

Note: I implemented the circuit in CMOS 0.35 technology.

Thanks.

-I used PVT independent Schmitt trigger (ST) with fully adjustable threshold voltage to mitigate the modulated signal delay, but the ST does not work in delay mitigation.

Please comment: Is PVT-independent ST a wise choice to mitigate signal delay? How can o get PVT-independent modulated signal?

Note: I implemented the circuit in CMOS 0.35 technology.

Thanks.