mango21

Newbie

Hi all,

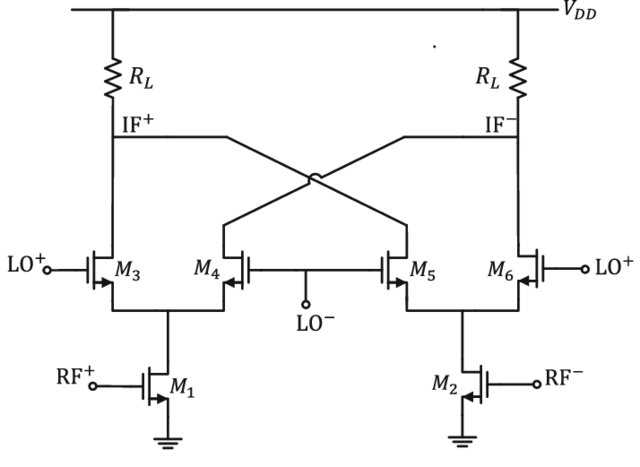

I'm designing a CMOS gilbert cell mixer and having now problem of setting the DC bias voltage of the LO port.

I've read some threads regarding this problem in this forum, my understanding on this is: the switching quad(M3-M6) should be biased at Vgs≈Vth to make sure that the transistors turn on for half period and turn off for the rest half period. And because I want them to work as good switches, their Vds should stay low so that once the transistors turn on, they go quickly into triode region? Am I right?

Thanks for the opinions in advance!

I'm designing a CMOS gilbert cell mixer and having now problem of setting the DC bias voltage of the LO port.

I've read some threads regarding this problem in this forum, my understanding on this is: the switching quad(M3-M6) should be biased at Vgs≈Vth to make sure that the transistors turn on for half period and turn off for the rest half period. And because I want them to work as good switches, their Vds should stay low so that once the transistors turn on, they go quickly into triode region? Am I right?

Thanks for the opinions in advance!