yefj

Advanced Member level 5

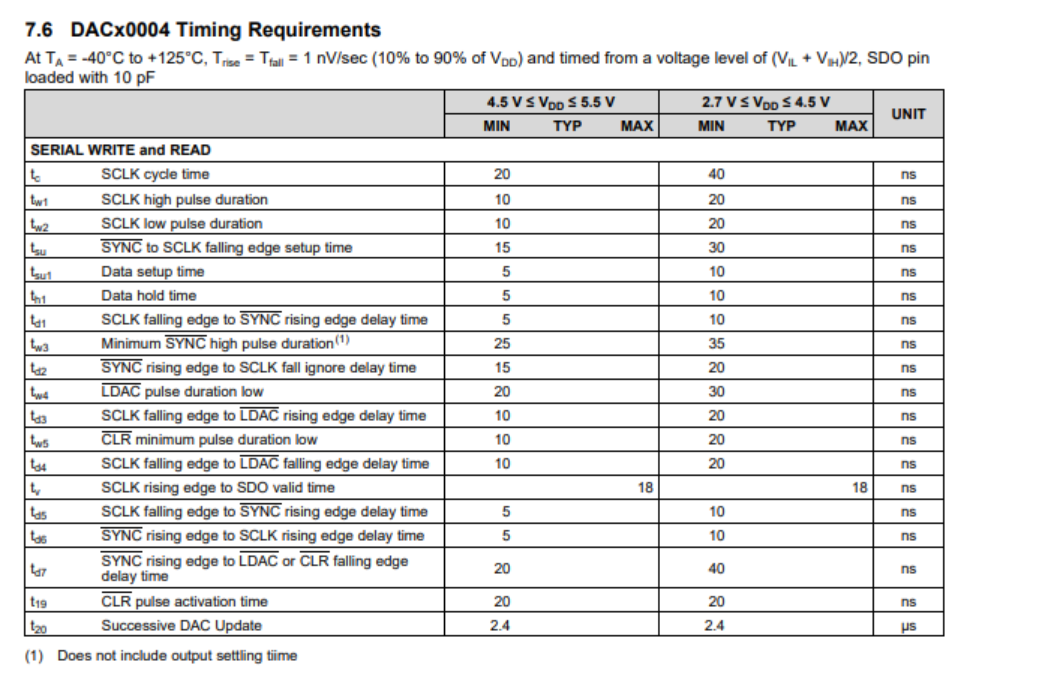

Hello ,In the datasheet shown bellow we have a table of timing requirements.

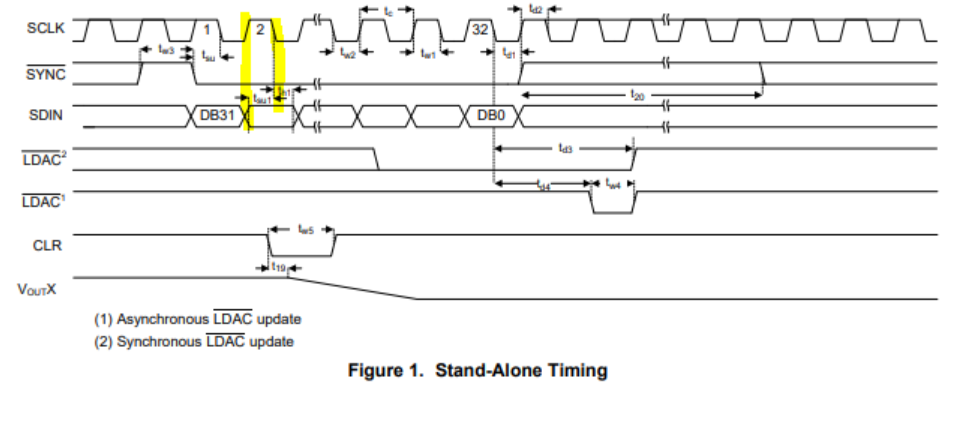

I cant see from the table and from the diagram bellow why i should complute my SPI with sampling in FALLING EDGE?

if you could please draw the arrrow up and down on the diagram so i understand why they want a falling edge samplin?

because as i can see the clock could be both on rising and falling in this place.

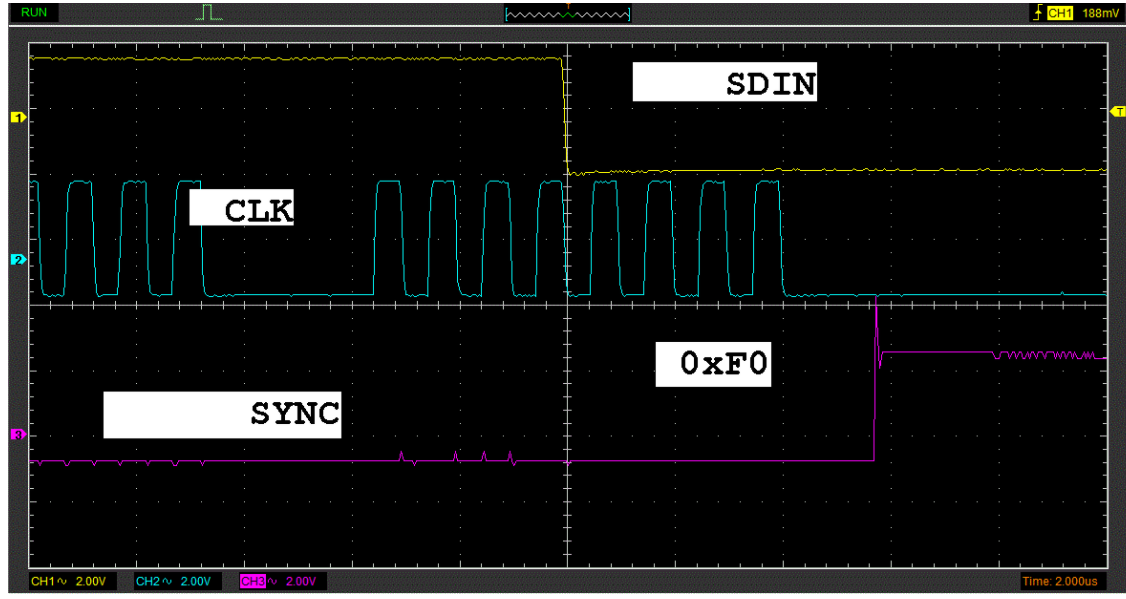

In the photo shown bellow there is a photo of my SPI sequence,How can i see visualy that it sampling or rising edge?

Thanks.

I cant see from the table and from the diagram bellow why i should complute my SPI with sampling in FALLING EDGE?

if you could please draw the arrrow up and down on the diagram so i understand why they want a falling edge samplin?

because as i can see the clock could be both on rising and falling in this place.

In the photo shown bellow there is a photo of my SPI sequence,How can i see visualy that it sampling or rising edge?

Thanks.

Last edited: