AllenD

Member level 5

Hi All,

Can I please ask some help about clock design.

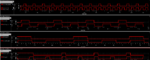

In the attached picture there are 4 clock plots. For each one of the clock plot, there are 2 clocks signals(8 clocks scheme in total but they are sorts of similar). The upper one is the goal and lower one is what I have for now. Basically, I want to make every other clock high disappear.

Can you please let me know how to generate the upper clock from the lower clock?