ASIC_intl

Banned

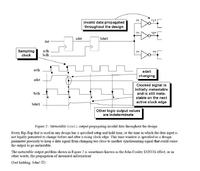

Sometimes we transfer data from one clock domain to anothe using a fifo. Is it (transferring data from one clock domain to another clock domain by using a FIFO) only done when write clock cycle is faster than the read clock cycle? Or, It can also be done when write clock cycle is faster than read clock cycle.