__apotamkin

Newbie

I am writing a clock divider to get 10sec, 8sec, 3 sec from 50 Mhz clock signal.

This is my main module code :

And this is the test bench code:

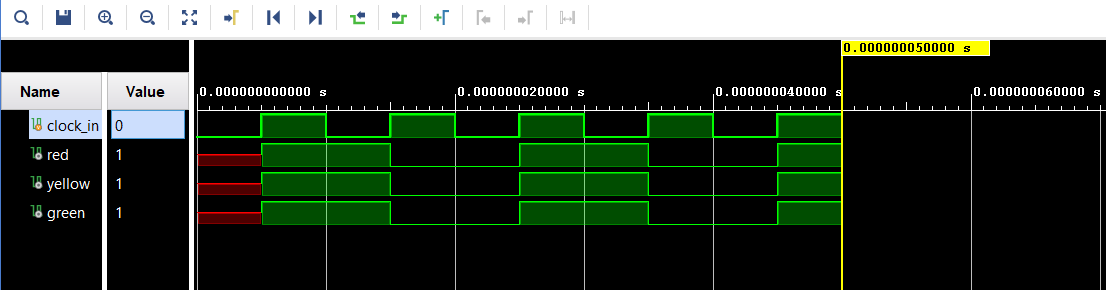

This is the simulation

I set simulation time to 50 from simulation settings and when I look at the simulation, end of the diagram is 0.000000050000s as you can see. Why it doesn't look like just 50s ? How can I fix this?

This is my main module code :

Code Verilog - [expand]

And this is the test bench code:

Code Verilog - [expand]

This is the simulation

I set simulation time to 50 from simulation settings and when I look at the simulation, end of the diagram is 0.000000050000s as you can see. Why it doesn't look like just 50s ? How can I fix this?

Last edited by a moderator: