tnnedaboard

Member level 3

Hello everyone,

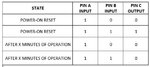

I have to make a small circuit with an integrated FLIP FLOP that has this function:

1. pin A and B input to 1, pin C output goes to 1

2. when pin A is 1 and pin B is 0, pin C goes to 0 and remains there even if pin B returns to 1

3. pin C returns to 1 only when pin A goes from 1 to 0 and then to 1 again and with pin B to 1

how could I do? Help thanks.

I have to make a small circuit with an integrated FLIP FLOP that has this function:

1. pin A and B input to 1, pin C output goes to 1

2. when pin A is 1 and pin B is 0, pin C goes to 0 and remains there even if pin B returns to 1

3. pin C returns to 1 only when pin A goes from 1 to 0 and then to 1 again and with pin B to 1

how could I do? Help thanks.