pigtwo

Member level 4

Hello everyone,

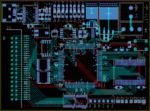

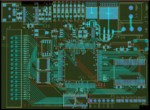

I just finished a circuit board and I am interested in getting a critique of the board/design. This is a personal project but the intention is to use this as example of my work to future employers. I would like to make this as professional looking as possible so if there are things that are not commonly done in professional circuit boards I'd love the know about it so I can correct it.

For context this board has a Spartan 6 with a PROM, SRAM, USB bridge, and ADC attached. The main output is driving a RGB led grid. The highest frequency(besides the USB) is 50 MHz. But few of the signals are driven anywhere close to this. This is my first attempt at really packing the components in as tightly as I could. (One dumb mistake I already noticed is for some reason I used 0805 parts when it was probably unnecessary.)

I've attached(I hope this is allowed) a .zip with the gerber files, a pdf of the schematic(for reference if you want), and the OrCAD .brd file if anyone uses OrCAD.

I welcome and appreciate any comments or recommendations.

Thank you!

I just finished a circuit board and I am interested in getting a critique of the board/design. This is a personal project but the intention is to use this as example of my work to future employers. I would like to make this as professional looking as possible so if there are things that are not commonly done in professional circuit boards I'd love the know about it so I can correct it.

For context this board has a Spartan 6 with a PROM, SRAM, USB bridge, and ADC attached. The main output is driving a RGB led grid. The highest frequency(besides the USB) is 50 MHz. But few of the signals are driven anywhere close to this. This is my first attempt at really packing the components in as tightly as I could. (One dumb mistake I already noticed is for some reason I used 0805 parts when it was probably unnecessary.)

I've attached(I hope this is allowed) a .zip with the gerber files, a pdf of the schematic(for reference if you want), and the OrCAD .brd file if anyone uses OrCAD.

I welcome and appreciate any comments or recommendations.

Thank you!