allennlowaton

Full Member level 5

Good day guys.

I badly need your ideas about this one.

I'm doing a charge pump. I'm amazed with what happened.

I change the time step on the transient analysis and it

yields different outputs.

I can't understand it.

Please refer to the figures below:

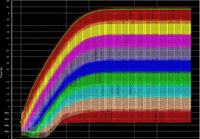

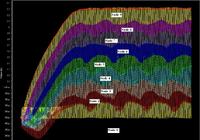

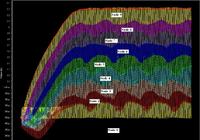

1. This one is the result of this transient analysis

.tran 100us 400ms

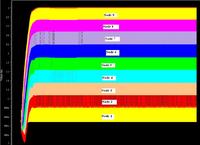

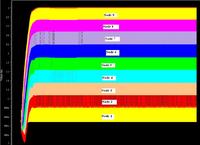

2. This one is the result of this transient analysis

.tran 1ms 400ms

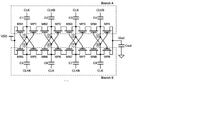

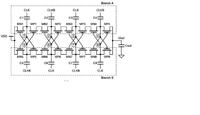

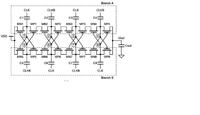

This is the circuit of this simulation. It shows only the 4 stage but I simulated 9 stages.

The time step with 100us yields a 3v output

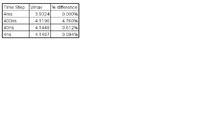

But, the time step with 1ms yields only 2.4v....

Help please............

I badly need your ideas about this one.

I'm doing a charge pump. I'm amazed with what happened.

I change the time step on the transient analysis and it

yields different outputs.

I can't understand it.

Please refer to the figures below:

1. This one is the result of this transient analysis

.tran 100us 400ms

2. This one is the result of this transient analysis

.tran 1ms 400ms

This is the circuit of this simulation. It shows only the 4 stage but I simulated 9 stages.

The time step with 100us yields a 3v output

But, the time step with 1ms yields only 2.4v....

Help please............