Mabrok

Full Member level 4

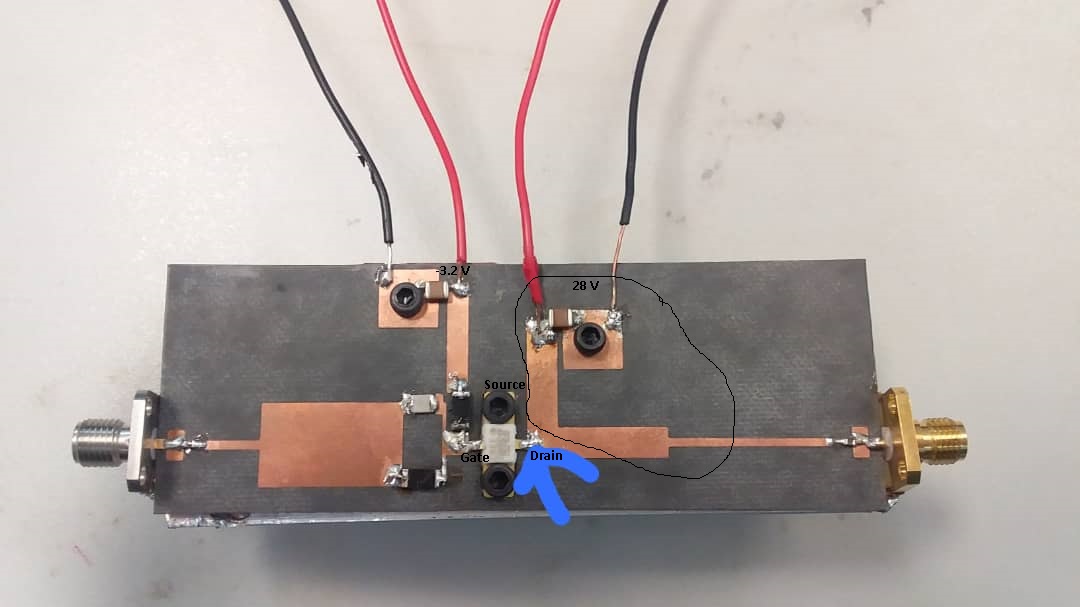

I have used CGH40010F transistor provided by cree in real fabricated design. during the testing and connecting the DC power supplies to drain and gate terminals. Once I switch on power supply i got short at the drain terminal (circled one in the attached image). Also, drain terminal where i have to connect positive side of the dc power supply, this side connected to the ground when testing with multi meter (test for continuity). This is because the drain terminal and source they are connected when check for continuity (the transistor it self before soldering). So, after soldering the drain side to the circled side highlighted in the attached photo. The whole circled side become ground as the source connected to the ground. please

advice me about this as this is my first time doing real experiment. Thank you

advice me about this as this is my first time doing real experiment. Thank you