mahmoud_Esmail

Newbie level 4

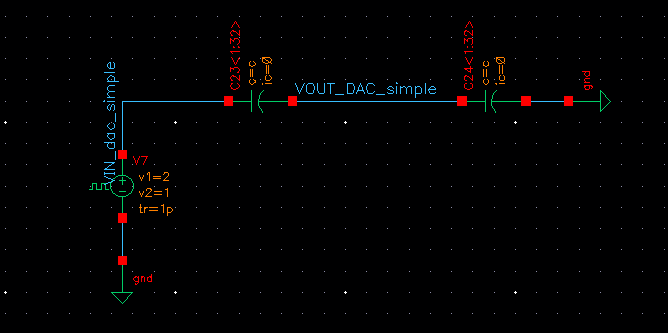

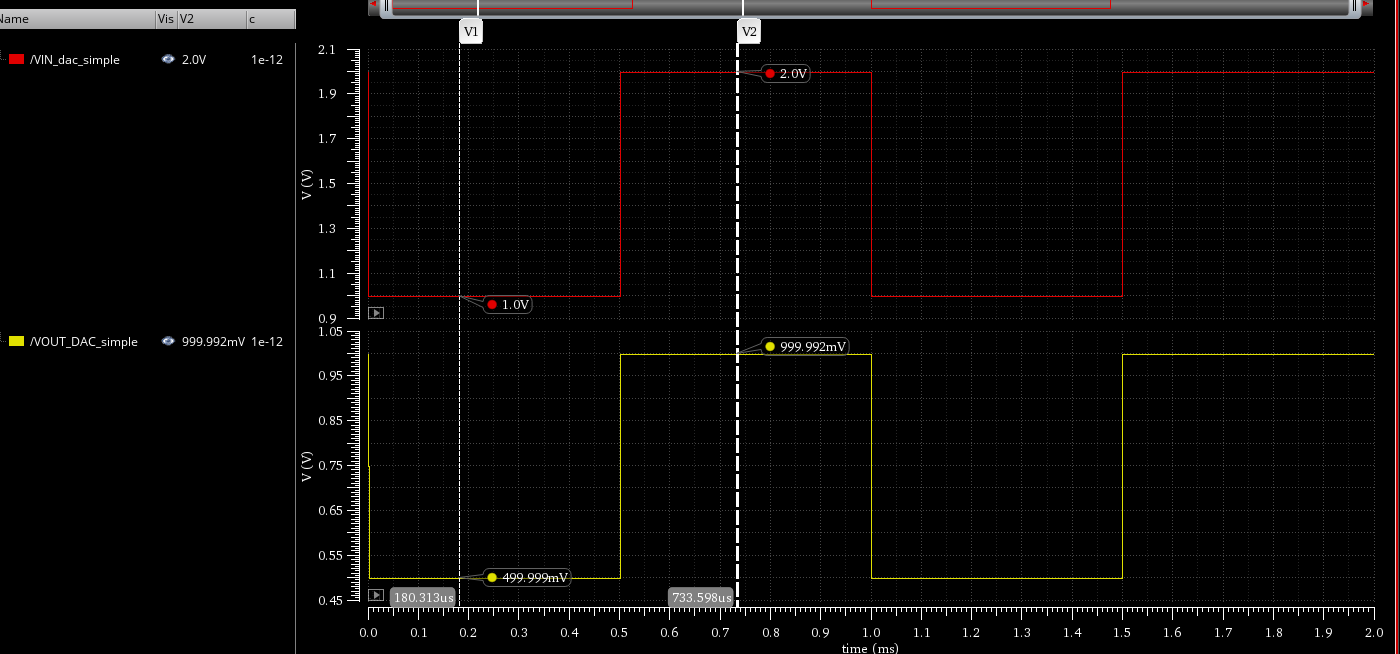

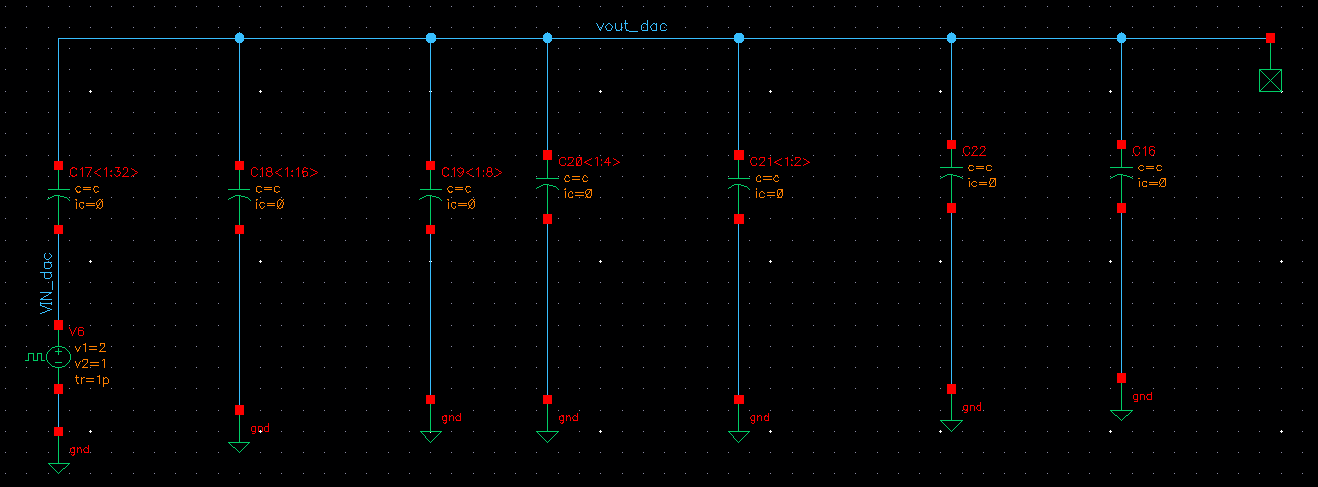

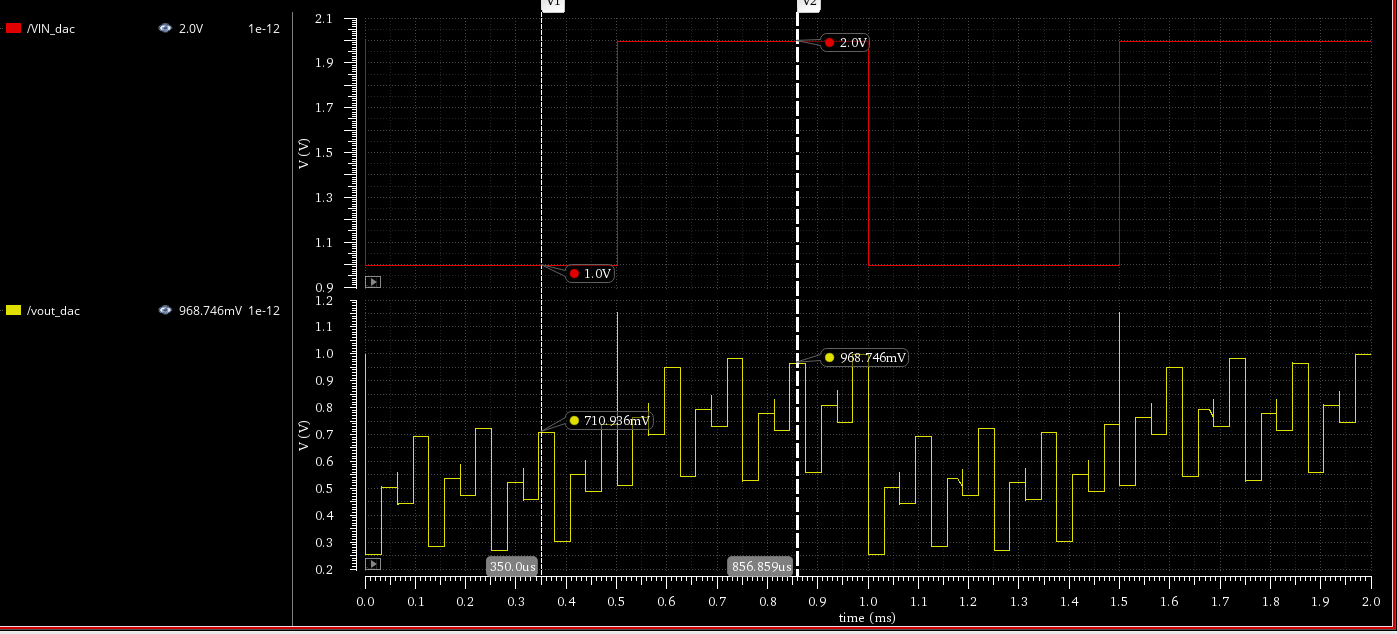

I am simulating CDAC but you can think of it as cap. voltage divider issue , I did two simulations the first is for a very simple CAP. voltage divider [attached schematic] everything works fine after I set zero IC conditions on the caps , the output should be half the input which is verified using the a simulation [attached waveform] , the second simulation is bigger circuit [attached schematic ] but it really the equivalent of first schematic if you take the caps on the right in parallel , you would expect the output voltage to be half the input voltage as first case but some strange stuff is there [ attached waveforms] the output is changing while the input is constant to some strange values , I don't know what is problem as two schematics as equivalent . I am using unit cap. of 1p F then array of caps. is formed , the frequency of the input 1khz and rise and fall times are 1fs.