AMSA84

Advanced Member level 2

- Joined

- Aug 24, 2010

- Messages

- 577

- Helped

- 8

- Reputation

- 16

- Reaction score

- 8

- Trophy points

- 1,298

- Location

- Iberian Peninsula

- Activity points

- 6,178

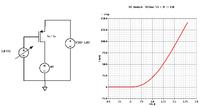

Has the title says, I am not being sucessful on plotting the I-V characteristic of a PMOS transistor, using cadence.

Can someone give me a tip on how to do it?

Kind regards.

Can someone give me a tip on how to do it?

Kind regards.