goatmxj666

Member level 3

Hello

I want to export the gds of an on-chip transformer layout and import it into hfss for EM simulation.

After importing the gds in HFSS, I also imported the layer.map file to get the layer information.

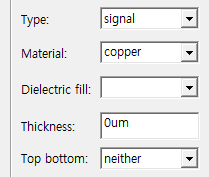

However, there is no thickness information as shown in the picture below.

I checked that the '.tf' file provided by TSMC also has no thickness information.

The pdk only shows the thickness information of M1-M5.

I need to know the thickness of the via between M1-M5 so that I can enter the thickness information in hfss properly.

If anyone knows how to do this, please help me.

Thanks.

I want to export the gds of an on-chip transformer layout and import it into hfss for EM simulation.

After importing the gds in HFSS, I also imported the layer.map file to get the layer information.

However, there is no thickness information as shown in the picture below.

I checked that the '.tf' file provided by TSMC also has no thickness information.

The pdk only shows the thickness information of M1-M5.

I need to know the thickness of the via between M1-M5 so that I can enter the thickness information in hfss properly.

If anyone knows how to do this, please help me.

Thanks.