tiwari.sachin

Full Member level 6

I am using a BGA and unable to understand how to route the decaps of power line

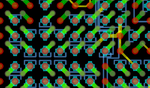

Ideally as shown in image below FPGA_3V3 should go to decap first and then to active part (FPGA Power)

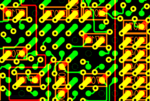

Due to space constraints and fan out taken, I have a via between active part and decap and that via connects to FPGA_3V3 and thereby the entire idea of having a decap seems to go for a toss.

Image 3 shows how the decap is connected.

Can anyone suggest me the best way to route the decaps.

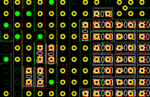

Since there are a lot of them (on FPGA_3V3, FPGA_2V5 and FPGA_1V1), i had planned to keep FPGA on Top layer and Decaps (0402) and bottom. I hardly have a option to use both on same layer.

Ideally as shown in image below FPGA_3V3 should go to decap first and then to active part (FPGA Power)

Due to space constraints and fan out taken, I have a via between active part and decap and that via connects to FPGA_3V3 and thereby the entire idea of having a decap seems to go for a toss.

Image 3 shows how the decap is connected.

Can anyone suggest me the best way to route the decaps.

Since there are a lot of them (on FPGA_3V3, FPGA_2V5 and FPGA_1V1), i had planned to keep FPGA on Top layer and Decaps (0402) and bottom. I hardly have a option to use both on same layer.