rishubnagpal

Newbie

Dear all,

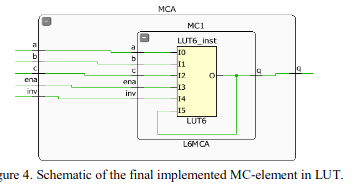

I'm attempting to instantiate a Muller C-element based on the work done by [1]. Briefly, this gate only changes its value when both inputs are equal, otherwise it holds its previous value. In the below figure, there is a feedback path from the output O of the LUT to the input I5. Does this path need to be constrained? If so, what would be the best way to do so? The paper gives some timing info for this gate:

" The minimal calculated delay per one single element (including LUT and interconnects) was 491 ps, the maximal value was 713 ps. "

This EE stackexchange answer [2] alludes to a constraint on the feedback path, but there isn't enough detail for me to proceed forward.

Thanks in advance for any insight on this.

[1]: http://dspace5.zcu.cz/bitstream/11025/35432/1/Pfeifer2.pdf

[2]: http://electronics.stackexchange.com/a/222450

Note, this quesiton was crossposted from the xilinx forum here: http://support.xilinx.com/s/questio...-a-combinatorial-feedback-path?language=en_US

I'm attempting to instantiate a Muller C-element based on the work done by [1]. Briefly, this gate only changes its value when both inputs are equal, otherwise it holds its previous value. In the below figure, there is a feedback path from the output O of the LUT to the input I5. Does this path need to be constrained? If so, what would be the best way to do so? The paper gives some timing info for this gate:

" The minimal calculated delay per one single element (including LUT and interconnects) was 491 ps, the maximal value was 713 ps. "

This EE stackexchange answer [2] alludes to a constraint on the feedback path, but there isn't enough detail for me to proceed forward.

Thanks in advance for any insight on this.

[1]: http://dspace5.zcu.cz/bitstream/11025/35432/1/Pfeifer2.pdf

[2]: http://electronics.stackexchange.com/a/222450

Note, this quesiton was crossposted from the xilinx forum here: http://support.xilinx.com/s/questio...-a-combinatorial-feedback-path?language=en_US