vrefdesigner

Newbie

Hi everyone,

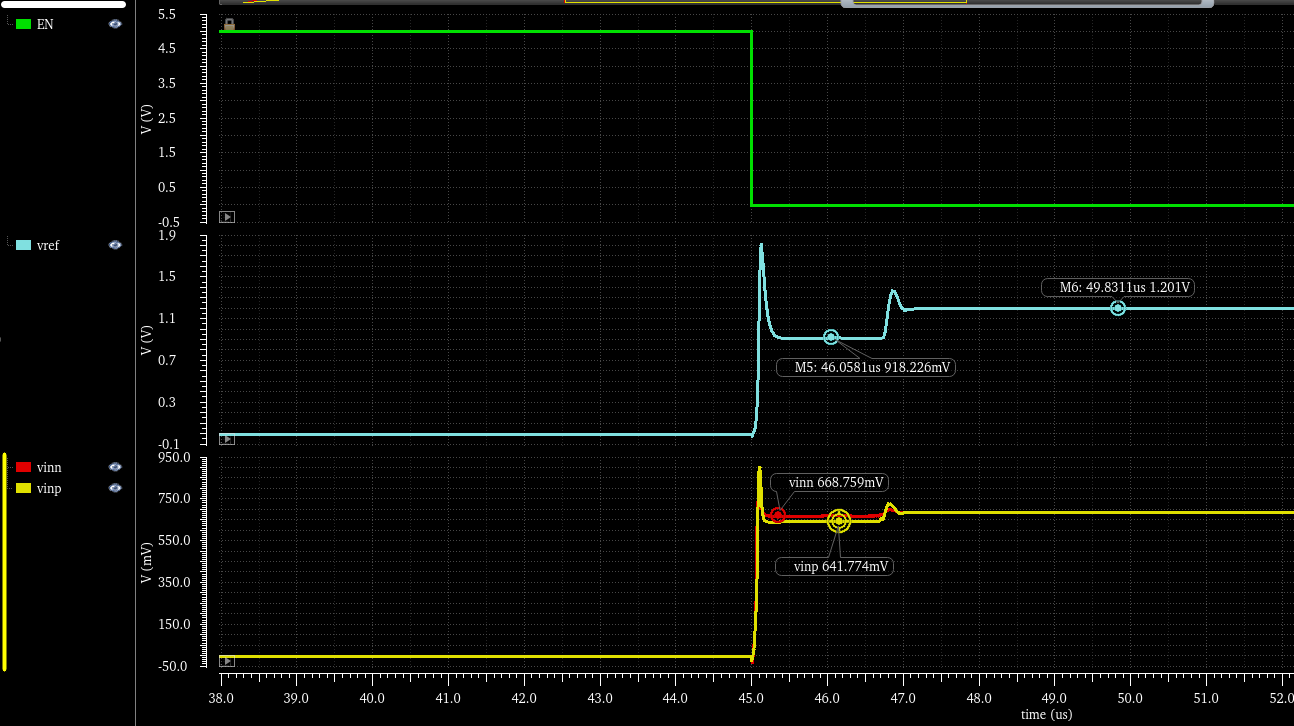

I'm designing an opamp-based beta-multiplier bandgap voltage reference with enable for thesis. However, I encountered a problem when enabling the vref from shutdown state (EN=1) to active state (EN=0). Please see simulation attached below.

As you can see, vref settles at 0.9V initially before fully settling to the correct value. I would like to know what the possible causes of the problem are. I'm thinking this is due to the charging of the BJT's parasitic caps and/or input pair's parasitic caps, but I'm not entirely sure/convinced it is the reason.

Info you may want:

* 8:1 BJT (5x5 unit area) ratio

* I_bjt=2uA

*

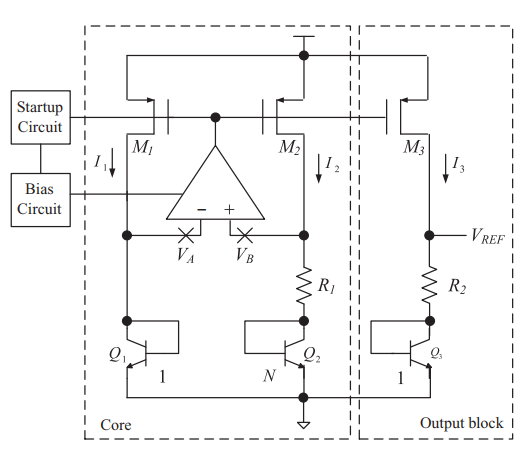

Bandgap vref architecture for reference

I'm designing an opamp-based beta-multiplier bandgap voltage reference with enable for thesis. However, I encountered a problem when enabling the vref from shutdown state (EN=1) to active state (EN=0). Please see simulation attached below.

As you can see, vref settles at 0.9V initially before fully settling to the correct value. I would like to know what the possible causes of the problem are. I'm thinking this is due to the charging of the BJT's parasitic caps and/or input pair's parasitic caps, but I'm not entirely sure/convinced it is the reason.

Info you may want:

* 8:1 BJT (5x5 unit area) ratio

* I_bjt=2uA

*

Bandgap vref architecture for reference